## ATmega16M1/ATmega32M1/ATmega64M1/ ATmega32C1/ATmega64C1 Automotive

## 8-bit Microcontroller with 16K/32K/64K Bytes In-system Programmable Flash

### **SUMMARY DATASHEET**

#### **Features**

- High performance, low power AVR® 8-bit microcontroller

- Advanced RISC architecture

- 131 powerful instructions most single clock cycle execution

- 32 × 8 general purpose working registers

- Fully static operation

- Up to 1MIPS throughput per MHz

- On-chip 2-cycle multiplier

- Data and non-volatile program memory

- 16K/32K/64K bytes flash of in-system programmable program memory

- Endurance: 10,000 write/erase cycles

- Optional boot code section with independent lock bits

- In-system programming by on-chip boot program

- True read-while-write operation

- 512/1024/2048 bytes of in-system programmable EEPROM

- Endurance: 100,000 write/erase cycles

- Programming lock for flash program and EEPROM data security

- 1024/2048/4096 bytes internal SRAM

- On chip debug interface (debugWIRE)

- CAN 2.0A/B with 6 message objects ISO 16845 certified (1)

- LIN 2.1 and 1.3 controller or 8-Bit UART

- One 12-bit high speed PSC (power stage controller) (only ATmega16/32/64M1)

- Non overlapping inverted PWM output pins with flexible dead-time

- Variable PWM duty cycle and frequency

- Synchronous update of all PWM registers

- Auto stop function for emergency event

- Peripheral features

- One 8-bit general purpose Timer/Counter with separate prescaler, compare mode and capture mode

- One 16-bit general purpose Timer/Counter with separate prescaler, compare mode and capture mode

This is a summary document. The complete document is available on the Atmel website at www.atmel.com.

1. See certification on Atmel<sup>®</sup> web site.

- One master/slave SPI serial interface

- 10-bit ADC

- Up To 11 single ended channels and 3 fully differential ADC channel pairs

- Programmable gain (5x, 10x, 20x, 40x) on differential channels

- Internal reference voltage

- Direct power supply voltage measurement

- 10-bit DAC for variable voltage reference (comparators, ADC)

- Four analog comparators with variable threshold detection

- 100µA ±6% current source (LIN node identification)

- Interrupt and wake-up on pin change

- · Programmable watchdog timer with separate on-chip oscillator

- On-chip temperature sensor

- Special microcontroller features

- Low power idle, noise reduction, and power down modes

- Power on reset and programmable brown out detection

- In-system programmable via SPI port

- High precision crystal oscillator for CAN operations (16MHz)

- Internal calibrated RC oscillator (8MHz)

- On-chip PLL for fast PWM (32MHz, 64MHz) and CPU (16MHz) (only ATmega16/32/64M1)

- Operating voltage:

- 2.7V 5.5V

- Extended operating temperature:

- –40°C to +125°C

- · Core speed grade:

- 0 8MHz at 2.7 4.5V

- 0 16MHz at 4.5 5.5V

Table 1. ATmega32/64/M1/C1 Product Line-up

| Part Number          | ATmega32C1 | ATmega64C1 | ATmega16M1                  | ATmega32M1 | ATmega64M1 |  |  |  |  |

|----------------------|------------|------------|-----------------------------|------------|------------|--|--|--|--|

| Flash size           | 32 Kbyte   | 64 Kbyte   | 16 Kbyte                    | 32 Kbyte   | 64 Kbyte   |  |  |  |  |

| RAM size             | 2048 bytes | 4096 bytes | 1024 bytes                  | 2048 bytes | 4096 bytes |  |  |  |  |

| EEPROM size          | 1024 bytes | 2048 bytes | 512 bytes                   | 1024 bytes | 2048 bytes |  |  |  |  |

| 8-bit timer          |            |            | Yes                         |            |            |  |  |  |  |

| 16-bit timer         |            |            | Yes                         |            |            |  |  |  |  |

| PSC                  | N          | lo         |                             | Yes        |            |  |  |  |  |

| PWM outputs          | 4          | 4          | 10                          | 10         | 10         |  |  |  |  |

| Fault inputs (PSC)   | 0          | 0          | 3                           | 3          | 3          |  |  |  |  |

| PLL                  | N          | lo         |                             | Yes        |            |  |  |  |  |

| 10-bit ADC channels  |            |            | 11 single<br>3 differential |            |            |  |  |  |  |

| 10-bit DAC           |            |            | Yes                         |            |            |  |  |  |  |

| Analog comparators   |            |            | 4                           |            |            |  |  |  |  |

| Current source       |            |            | Yes                         |            |            |  |  |  |  |

| CAN                  |            |            | Yes                         |            |            |  |  |  |  |

| LIN/UART             |            | Yes        |                             |            |            |  |  |  |  |

| On-chip temp. sensor |            | Yes        |                             |            |            |  |  |  |  |

| SPI interface        |            |            | Yes                         |            |            |  |  |  |  |

## 1. Pin Configurations

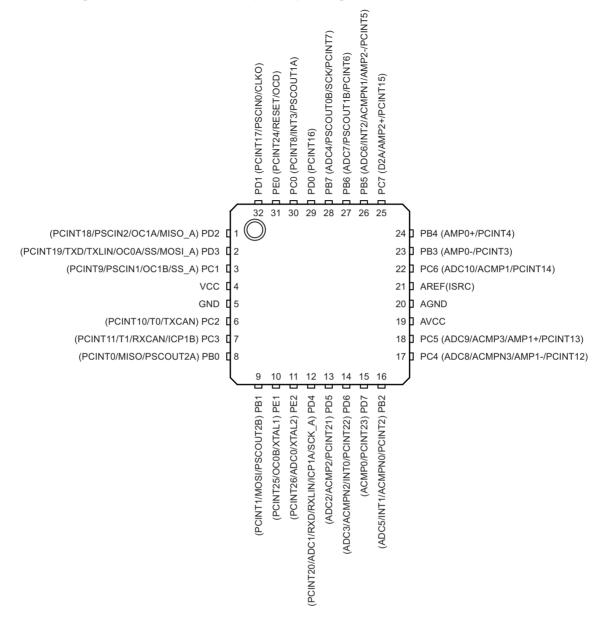

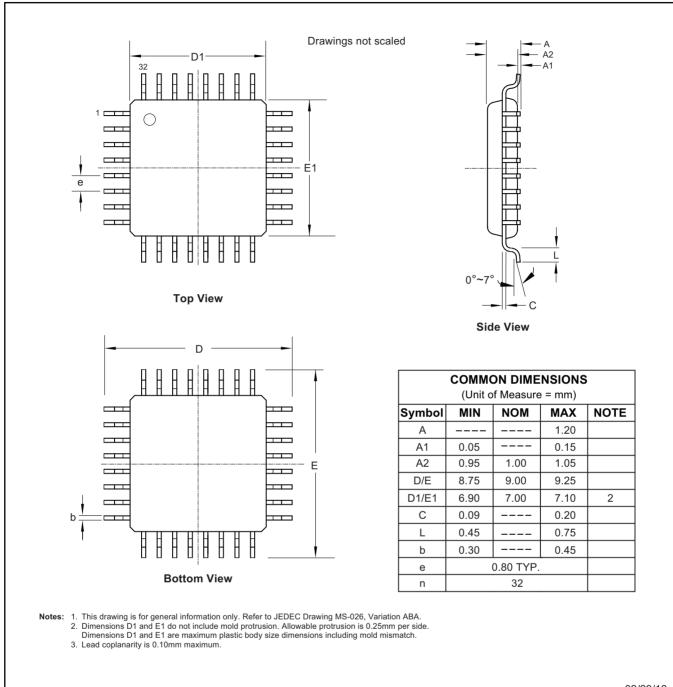

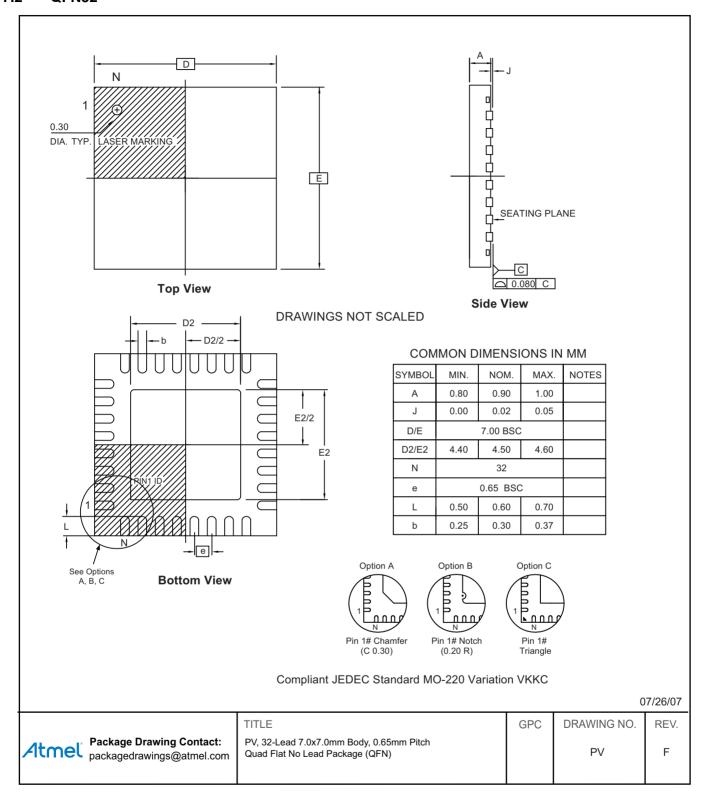

Figure 1-1. ATmega16/32/64M1 TQFP32/QFN32 (7\*7mm) Package

Note: On the engineering samples (parts marked AT90PWM324), the ACMPN3 alternate function is not located on PC4. It is located on PE2.

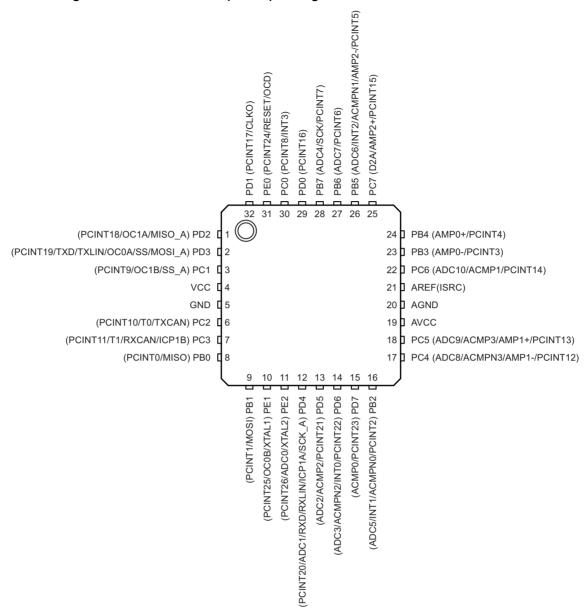

Figure 1-2. ATmega32/64C1 TQFP32/QFN32 (7\*7mm) Package

Note: On the first engineering samples (parts marked AT90PWM324), the ACMPN3 alternate function is not located on PC4. It is located on PE2.

#### **Pin Descriptions** 1.1

Table 1-1. Pin-out Description

| QFN32 Pin<br>Number | Mnemonic         | Туре                | Name, Function and Alternate Function                                                                                                           |

|---------------------|------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 5                   | GND              | Power               | Ground: 0V reference                                                                                                                            |

| 20                  | AGND             | Power               | Analog Ground: 0V reference for analog part                                                                                                     |

| 4                   | VCC              | Power               | Power supply                                                                                                                                    |

| 40                  | A) (C) C         | Dawar               | Analog Power Supply: This is the power supply voltage for analog part                                                                           |

| 19                  | AVCC             | Power               | For a normal use this pin must be connected.                                                                                                    |

| 21                  | AREF             | Power               | Analog Reference: Reference for analog converter. This is the reference voltage of the A/D converter. As output, can be used by external analog |

|                     |                  |                     | ISRC (Current Source Output)                                                                                                                    |

|                     |                  |                     | MISO (SPI Master In Slave Out)                                                                                                                  |

| 8                   | PB0              | I/O                 | PSCOUT2A (PSC Module 2 Output A)                                                                                                                |

|                     |                  |                     | PCINT0 (Pin Change Interrupt 0)                                                                                                                 |

|                     |                  |                     | MOSI (SPI Master Out Slave In)                                                                                                                  |

| 9                   | PB1              | I/O                 | PSCOUT2B (PSC Module 2 Output B)                                                                                                                |

|                     |                  |                     | PCINT1 (Pin Change Interrupt 1)                                                                                                                 |

|                     |                  |                     | ADC5 (Analog Input Channel 5)                                                                                                                   |

| 16                  | PB2              | I/O                 | INT1 (External Interrupt 1 Input)                                                                                                               |

| 10                  |                  |                     | ACMPN0 (Analog Comparator 0 Negative Input)                                                                                                     |

|                     |                  |                     | PCINT2 (Pin Change Interrupt 2)                                                                                                                 |

| 23                  | PB3              | I/O                 | AMP0- (Analog Differential Amplifier 0 Negative Input)                                                                                          |

| 23                  | PBS              | 1/0                 | PCINT3 (Pin Change Interrupt 3)                                                                                                                 |

| 24                  | PB4              | I/O                 | AMP0+ (Analog Differential Amplifier 0 Positive Input)                                                                                          |

| 24                  | F D4             | 1/0                 | PCINT4 (Pin Change Interrupt 4)                                                                                                                 |

|                     |                  |                     | ADC6 (Analog Input Channel 6)                                                                                                                   |

|                     |                  |                     | INT2 (External Interrupt 2 Input)                                                                                                               |

| 26                  | PB5              | I/O                 | ACMPN1 (Analog Comparator 1 Negative Input)                                                                                                     |

|                     |                  |                     | AMP2- (Analog Differential Amplifier 2 Negative Input)                                                                                          |

|                     |                  |                     | PCINT5 (Pin Change Interrupt 5)                                                                                                                 |

|                     |                  |                     | ADC7 (Analog Input Channel 7)                                                                                                                   |

| 27                  | PB6              | I/O                 | PSCOUT1B (PSC Module 1 Output A)                                                                                                                |

|                     |                  |                     | PCINT6 (Pin Change Interrupt 6)                                                                                                                 |

|                     |                  |                     | ADC4 (Analog Input Channel 4)                                                                                                                   |

| 20                  | DDZ              | 1/0                 | PSCOUT0B (PSC Module 0 Output B)                                                                                                                |

| 28                  | PB7              | I/O                 | SCK (SPI Clock)                                                                                                                                 |

|                     |                  |                     | PCINT7 (Pin Change Interrupt 7)                                                                                                                 |

|                     |                  |                     | PSCOUT1A (PSC Module 1 Output A)                                                                                                                |

| 30                  | PC0              | I/O                 | INT3 (External Interrupt 3 Input)                                                                                                               |

|                     |                  |                     | PCINT8 (Pin Change Interrupt 8)                                                                                                                 |

| Note: 1 Or          | the first angine | vina a campula a (v |                                                                                                                                                 |

Note: 1. On the first engineering samples (parts marked AT90PWM324), the ACMPN3 alternate function is not located on PC4. It is located on PE2.

Table 1-1. Pin-out Description (Continued)

| QFN32 Pin<br>Number | Mnemonic | Туре | Name, Function and Alternate Function                                                                   |  |  |  |  |

|---------------------|----------|------|---------------------------------------------------------------------------------------------------------|--|--|--|--|

|                     |          | 7.   | PSCIN1 (PSC Digital Input 1)                                                                            |  |  |  |  |

|                     |          |      | OC1B (Timer 1 Output Compare B)                                                                         |  |  |  |  |

| 3                   | PC1      | I/O  | SS_A (Alternate SPI Slave Select)                                                                       |  |  |  |  |

|                     |          |      | PCINT9 (Pin Change Interrupt 9)                                                                         |  |  |  |  |

|                     |          |      | T0 (Timer 0 clock input)                                                                                |  |  |  |  |

| 6                   | PC2      | I/O  | TXCAN (CAN Transmit Output)                                                                             |  |  |  |  |

|                     |          |      | PCINT10 (Pin Change Interrupt 10)                                                                       |  |  |  |  |

|                     |          |      | T1 (Timer 1 clock input)                                                                                |  |  |  |  |

| -                   | DOO      | 1/0  | RXCAN (CAN Receive Input)                                                                               |  |  |  |  |

| 7                   | PC3      | I/O  | ICP1B (Timer 1 input capture alternate B input)                                                         |  |  |  |  |

|                     |          |      | PCINT11 (Pin Change Interrupt 11)                                                                       |  |  |  |  |

|                     |          |      | ADC8 (Analog Input Channel 8)                                                                           |  |  |  |  |

| 47                  | DO4      | 1/0  | AMP1- (Analog Differential Amplifier 1 Negative Input)                                                  |  |  |  |  |

| 17                  | PC4      | I/O  | ACMPN3 (Analog Comparator 3 Negative Input)                                                             |  |  |  |  |

|                     |          |      | PCINT12 (Pin Change Interrupt 12)                                                                       |  |  |  |  |

|                     |          |      | ADC9 (Analog Input Channel 9)                                                                           |  |  |  |  |

| 40                  | DOF      | I/O  | AMP1+ (Analog Differential Amplifier 1 Positive Input)                                                  |  |  |  |  |

| 18                  | PC5      |      | ACMP3 (Analog Comparator 3 Positive Input)                                                              |  |  |  |  |

|                     |          |      | PCINT13 (Pin Change Interrupt 13)                                                                       |  |  |  |  |

|                     |          |      | ADC10 (Analog Input Channel 10)                                                                         |  |  |  |  |

| 22                  | PC6      | I/O  | ACMP1 (Analog Comparator 1 Positive Input)                                                              |  |  |  |  |

|                     |          |      | PCINT14 (Pin Change Interrupt 14)                                                                       |  |  |  |  |

|                     |          |      | D2A (DAC output)                                                                                        |  |  |  |  |

| 25                  | PC7      | I/O  | AMP2+ (Analog Differential Amplifier 2 Positive Input)                                                  |  |  |  |  |

|                     |          |      | PCINT15 (Pin Change Interrupt 15)                                                                       |  |  |  |  |

| 29                  | PD0      | I/O  | PSCOUT0A (PSC Module 0 Output A)                                                                        |  |  |  |  |

| 29                  | 1 00     | 1/0  | PCINT16 (Pin Change Interrupt 16)                                                                       |  |  |  |  |

|                     |          |      | PSCIN0 (PSC Digital Input 0)                                                                            |  |  |  |  |

| 32                  | PD1      | I/O  | CLKO (System Clock Output)                                                                              |  |  |  |  |

|                     |          |      | PCINT17 (Pin Change Interrupt 17)                                                                       |  |  |  |  |

|                     |          |      | OC1A (Timer 1 Output Compare A)                                                                         |  |  |  |  |

| 1                   | PD2      | I/O  | PSCIN2 (PSC Digital Input 2)                                                                            |  |  |  |  |

| •                   | 1 02     | 1/0  | MISO_A (Programming & alternate SPI Master In Slave Out)                                                |  |  |  |  |

|                     |          |      | PCINT18 (Pin Change Interrupt 18)                                                                       |  |  |  |  |

|                     |          |      | TXD (UART Tx data)                                                                                      |  |  |  |  |

|                     |          |      | TXLIN (LIN Transmit Output)                                                                             |  |  |  |  |

| 2                   | PD3      | I/O  | OC0A (Timer 0 Output Compare A)                                                                         |  |  |  |  |

| _                   | 1 03     | 1/0  | SS (SPI Slave Select)                                                                                   |  |  |  |  |

|                     |          |      | MOSI_A (Programming & alternate Master Out SPI Slave In)                                                |  |  |  |  |

| Note: 1. Or         |          |      | PCINT19 (Pin Change Interrupt 19) arts marked AT90PWM324), the ACMPN3 alternate function is not located |  |  |  |  |

Note: 1. On the first engineering samples (parts marked AT90PWM324), the ACMPN3 alternate function is not located on PC4. It is located on PE2.

Table 1-1. Pin-out Description (Continued)

| QFN32 Pin<br>Number | Mnemonic | Туре     | Name, Function and Alternate Function           |

|---------------------|----------|----------|-------------------------------------------------|

|                     |          |          | ADC1 (Analog Input Channel 1)                   |

|                     |          |          | RXD (UART Rx data)                              |

| 12                  | PD4      | I/O      | RXLIN (LIN Receive Input)                       |

| 12                  | 1 54     | 1/0      | ICP1A (Timer 1 input capture alternate A input) |

|                     |          |          | SCK_A (Programming & alternate SPI Clock)       |

|                     |          |          | PCINT20 (Pin Change Interrupt 20)               |

|                     |          |          | ADC2 (Analog Input Channel 2)                   |

| 13                  | PD5      | I/O      | ACMP2 (Analog Comparator 2 Positive Input)      |

|                     |          |          | PCINT21 (Pin Change Interrupt 21)               |

|                     |          | I/O      | ADC3 (Analog Input Channel 3)                   |

| 14                  | PD6      |          | ACMPN2 (Analog Comparator 2 Negative Input)     |

| 1-7                 |          |          | INT0 (External Interrupt 0 Input)               |

|                     |          |          | PCINT22 (Pin Change Interrupt 22)               |

| 15                  | PD7      | I/O      | ACMP0 (Analog Comparator 0 Positive Input)      |

| 10                  | 107      | 1,0      | PCINT23 (Pin Change Interrupt 23)               |

|                     |          |          | RESET (Reset Input)                             |

| 31                  | PE0      | I/O or I | OCD (On Chip Debug I/O)                         |

|                     |          |          | PCINT24 (Pin Change Interrupt 24)               |

|                     |          |          | XTAL1 (XTAL Input)                              |

| 10                  | PE1      | I/O      | OC0B (Timer 0 Output Compare B)                 |

|                     |          |          | PCINT25 (Pin Change Interrupt 25)               |

|                     |          |          | XTAL2 (XTAL Output)                             |

| 11                  | PE2      | I/O      | ADC0 (Analog Input Channel 0)                   |

|                     |          |          | PCINT26 (Pin Change Interrupt 26)               |

Note:

1. On the first engineering samples (parts marked AT90PWM324), the ACMPN3 alternate function is not located on PC4. It is located on PE2.

## 2. Overview

The Atmel<sup>®</sup> ATmega16/32/64/M1/C1 is a low-power CMOS 8-bit microcontroller based on the AVR enhanced RISC architecture. By executing powerful instructions in a single clock cycle, the Atmel ATmega16/32/64/M1/C1 achieves throughputs approaching 1MIPS per MHz allowing the system designer to optimize power consumption versus processing speed.

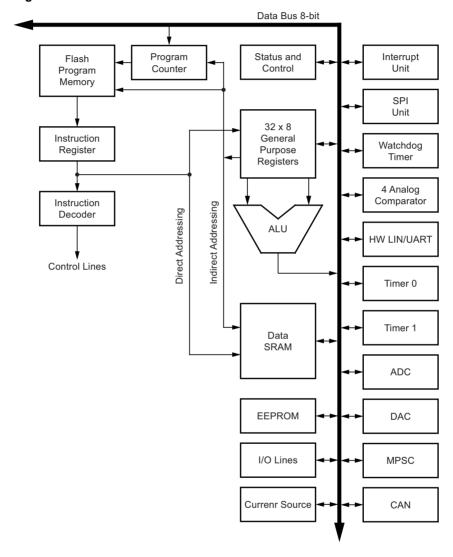

## 2.1 Block Diagram

Figure 2-1. Block Diagram

The AVR® core combines a rich instruction set with 32 general purpose working registers. All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle. The resulting architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.

The Atmel® ATmega16/32/64/M1/C1 provides the following features: 16K/32K/64K bytes of in-system programmable flash with read-while-write capabilities, 512/1024/2048 bytes EEPROM, 1024/2048/4096 bytes SRAM, 27 general purpose I/O lines, 32 general purpose working registers, one motor power stage controller, two flexible Timer/Counters with compare modes and PWM, one UART with HW LIN, an 11-channel 10-bit ADC with two differential input stages with programmable gain, a 10-bit DAC, a programmable watchdog timer with internal individual oscillator, an SPI serial port, an on-chip debug system and four software selectable power saving modes.

The idle mode stops the CPU while allowing the SRAM. Timer/Counters, SPI ports, CAN, LIN/UART and interrupt system to continue functioning. The power-down mode saves the register contents but freezes the oscillator, disabling all other chip functions until the next interrupt or hardware reset. The ADC noise reduction mode stops the CPU and all I/O modules except ADC, to minimize switching noise during ADC conversions. In standby mode, the crystal/resonator oscillator is running while the rest of the device is sleeping. This allows very fast start-up combined with low power consumption.

The device is manufactured using Atmel's high-density nonvolatile memory technology. The on-chip ISP flash allows the program memory to be reprogrammed in-system through an SPI serial interface, by a conventional nonvolatile memory programmer, or by an on-chip boot program running on the AVR core. The boot program can use any interface to download the application program in the application flash memory. Software in the boot flash section will continue to run while the application flash section is updated, providing true read-while-write operation. By combining an 8-bit RISC CPU with insystem self-programmable flash on a monolithic chip, the Atmel ATmega16/32/64/M1/C1 is a powerful microcontroller that provides a highly flexible and cost effective solution to many embedded control applications.

The ATmega16/32/64/M1/C1 AVR® is supported with a full suite of program and system development tools including: C compilers, macro assemblers, program debugger/simulators, in-circuit emulators, and evaluation kits.

#### 2.2 **Automotive Quality Grade**

The Atmel ATmega16/32/64/M1/C1 have been developed and manufactured according to the most stringent requirements of the international standard ISO-TS-16949. This data sheet contains limit values extracted from the results of extensive characterization (Temperature and Voltage). The quality and reliability of the ATmega16/32/64/M1/C1 have been verified during regular product qualification as per AEC-Q100 grade 1.

As indicated in the ordering information paragraph, the products are available in only one temperature grade.

Table 2-1. Temperature Grade Identification for Automotive Products

| Temperature   | Temperature Identifier | Comments                          |

|---------------|------------------------|-----------------------------------|

| –40°C; +125°C | Z                      | Full automotive temperature range |

#### 2.3 **Pin Descriptions**

#### 2.3.1 **VCC**

Digital supply voltage.

#### 2.3.2 **GND**

Ground.

#### Port B (PB7..PB0) 2.3.3

Port B is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The port B output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, port B pins that are externally pulled low will source current if the pull-up resistors are activated. The port B pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port B also serves the functions of various special features of the ATmega16/32/64/M1/C1.

#### 2.3.4 Port C (PC7..PC0)

Port C is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The port C output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, port C pins that are externally pulled low will source current if the pull-up resistors are activated. The port C pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port C also serves the functions of special features of the Atmel® ATmega16/32/64/M1/C1.

#### 2.3.5 Port D (PD7..PD0)

Port D is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The port D output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, port D pins that are externally pulled low will source current if the pull-up resistors are activated. The port D pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port D also serves the functions of various special features of the Atmel ATmega16/32/64/M1/C1.

#### Port E (PE2..0) RESET/ XTAL1/ XTAL2 2.3.6

Port E is an 3-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The port E output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, port E pins that are externally pulled low will source current if the pull-up resistors are activated. The port E pins are tri-stated when a reset condition becomes active, even if the clock is not running.

If the RSTDISBL fuse is programmed, PE0 is used as an I/O pin. Note that the electrical characteristics of PE0 differ from those of the other pins of port E.

If the RSTDISBL fuse is unprogrammed, PE0 is used as a reset input. A low level on this pin for longer than the minimum pulse length will generate a reset, even if the clock is not running.

Depending on the clock selection fuse settings, PE1 can be used as input to the inverting oscillator amplifier and input to the internal clock operating circuit.

Depending on the clock selection fuse settings, PE2 can be used as output from the inverting oscillator amplifier.

#### 2.3.7 **AVCC**

AVCC is the supply voltage pin for the A/D converter, D/A converter, current source. It should be externally connected to V<sub>CC</sub>, even if the ADC, DAC are not used. If the ADC is used, it should be connected to V<sub>CC</sub> through a low-pass filter.

#### 2.3.8 **AREF**

This is the analog reference pin for the A/D converter.

#### 2.4 **About Code Examples**

This documentation contains simple code examples that briefly show how to use various parts of the device. These code examples assume that the part specific header file is included before compilation. Be aware that not all C compiler vendors include bit definitions in the header files and interrupt handling in C is compiler dependent. Please confirm with the C compiler documentation for more details.

# 3. Instruction Set Summary

| Mnemonics     | Operands       | Description                               | Operation                                | Flags         | #Clocks |

|---------------|----------------|-------------------------------------------|------------------------------------------|---------------|---------|

| Arithmetic ar | nd Logic Instr | uctions                                   |                                          |               |         |

| ADD           | Rd, Rr         | Add two registers                         | Rd ← Rd + Rr                             | Z, C, N, V, H | 1       |

| ADC           | Rd, Rr         | Add with carry two registers              | $Rd \leftarrow Rd + Rr + C$              | Z, C, N, V, H | 1       |

| ADIW          | Rdl,K          | Add immediate to word                     | Rdh:Rdl ← Rdh:Rdl + K                    | Z, C, N, V, S | 2       |

| SUB           | Rd, Rr         | Subtract two registers                    | $Rd \leftarrow Rd - Rr$                  | Z, C, N, V, H | 1       |

| SUBI          | Rd, K          | Subtract constant from register           | $Rd \leftarrow Rd - K$                   | Z, C, N, V, H | 1       |

| SBC           | Rd, Rr         | Subtract with carry two registers         | $Rd \leftarrow Rd - Rr - C$              | Z, C, N, V, H | 1       |

| SBCI          | Rd, K          | Subtract with carry constant from reg.    | $Rd \leftarrow Rd - K - C$               | Z, C, N, V, H | 1       |

| SBIW          | Rdl,K          | Subtract immediate from word              | Rdh:Rdl ← Rdh:Rdl – K                    | Z, C, N, V, S | 2       |

| AND           | Rd, Rr         | Logical AND registers                     | $Rd \leftarrow Rd \times Rr$             | Z, N, V       | 1       |

| ANDI          | Rd, K          | Logical AND register and constant         | $Rd \leftarrow Rd \times K$              | Z, N, V       | 1       |

| OR            | Rd, Rr         | Logical OR registers                      | $Rd \leftarrow Rd \ v \ Rr$              | Z, N, V       | 1       |

| ORI           | Rd, K          | Logical OR register and constant          | Rd ← Rd v K                              | Z, N, V       | 1       |

| EOR           | Rd, Rr         | Exclusive OR registers                    | $Rd \leftarrow Rd \oplus Rr$             | Z, N, V       | 1       |

| COM           | Rd             | One's complement                          | Rd ← 0xFF – Rd                           | Z, C, N, V    | 1       |

| NEG           | Rd             | Two's complement                          | $Rd \leftarrow 0x00 - Rd$                | Z, C, N, V, H | 1       |

| SBR           | Rd,K           | Set bit(s) in register                    | Rd ← Rd v K                              | Z, N, V       | 1       |

| CBR           | Rd,K           | Clear bit(s) in register                  | $Rd \leftarrow Rd \cdot (0xFF - K)$      | Z, N, V       | 1       |

| INC           | Rd             | Increment                                 | Rd ← Rd + 1                              | Z, N, V       | 1       |

| DEC           | Rd             | Decrement                                 | Rd ← Rd – 1                              | Z, N, V       | 1       |

| TST           | Rd             | Test for zero or minus                    | $Rd \leftarrow Rd \times Rd$             | Z, N, V       | 1       |

| CLR           | Rd             | Clear register                            | $Rd \leftarrow Rd \oplus Rd$             | Z, N, V       | 1       |

| SER           | Rd             | Set register                              | Rd ← 0xFF                                | None          | 1       |

| MUL           | Rd, Rr         | Multiply unsigned                         | $R1:R0 \leftarrow Rd \times Rr$          | Z, C          | 2       |

| MULS          | Rd, Rr         | Multiply signed                           | $R1:R0 \leftarrow Rd \times Rr$          | Z, C          | 2       |

| MULSU         | Rd, Rr         | Multiply signed with unsigned             | $R1:R0 \leftarrow Rd \times Rr$          | Z, C          | 2       |

| FMUL          | Rd, Rr         | Fractional multiply unsigned              | R1:R0 ← (Rd x Rr) << 1                   | Z, C          | 2       |

| FMULS         | Rd, Rr         | Fractional multiply signed                | $R1:R0 \leftarrow (Rd \times Rr) << 1$   | Z, C          | 2       |

| FMULSU        | Rd, Rr         | Fractional multiply signed with unsigned  | R1:R0 ← (Rd x Rr) << 1                   | Z, C          | 2       |

| Branch Instr  | uctions        |                                           |                                          |               |         |

| RJMP          | k              | Relative jump                             | PC ← PC + k + 1                          | None          | 2       |

| IJMP          |                | Indirect jump to (Z)                      | PC ← Z                                   | None          | 2       |

| JMP(*)        | k              | Direct jump                               | PC ← k                                   | None          | 3       |

| RCALL         | k              | Relative subroutine call                  | PC ← PC + k + 1                          | None          | 3       |

| ICALL         |                | Indirect call to (Z)                      | PC ← Z                                   | None          | 3       |

| CALL(*)       | k              | Direct subroutine call                    | PC ← k                                   | None          | 4       |

| RET           |                | Subroutine return                         | PC ← STACK                               | None          | 4       |

| RETI          |                | Interrupt return                          | PC ← STACK                               | I             | 4       |

| CPSE          | Rd,Rr          | Compare, skip if equal                    | if (Rd = Rr) PC $\leftarrow$ PC + 2 or 3 | None          | 1/2/3   |

| Note: 1       | Those Inches   | uctions are only available in "16K and 32 | I/ marka"                                |               |         |

# 3. Instruction Set Summary (Continued)

| Mnemonics      | Operands        | Description                         | Operation                                                          | Flags         | #Clocks |

|----------------|-----------------|-------------------------------------|--------------------------------------------------------------------|---------------|---------|

| СР             | Rd,Rr           | Compare                             | Rd – Rr                                                            | Z, N, V, C, H | 1       |

| CPC            | Rd,Rr           | Compare with carry                  | Rd – Rr – C                                                        | Z, N, V, C, H | 1       |

| CPI            | Rd,K            | Compare register with immediate     | Rd – K                                                             | Z, N, V, C, H | 1       |

| SBRC           | Rr, b           | Skip if bit in register cleared     | if (Rr(b)=0) PC ← PC + 2 or 3                                      | None          | 1/2/3   |

| SBRS           | Rr, b           | Skip if bit in register is set      | if (Rr(b)=1) PC ← PC + 2 or 3                                      | None          | 1/2/3   |

| SBIC           | P, b            | Skip if bit in I/O register cleared | if (P(b)=0) PC ← PC + 2 or 3                                       | None          | 1/2/3   |

| SBIS           | P, b            | Skip if bit in I/O register is set  | if (P(b)=1) PC ← PC + 2 or 3                                       | None          | 1/2/3   |

| BRBS           | s, k            | Branch if status flag Set           | if (SREG(s) = 1) then PC $\leftarrow$ PC + k + 1                   | None          | 1/2     |

| BRBC           | s, k            | Branch if status flag cleared       | if (SREG(s) = 0) then PC $\leftarrow$ PC + k + 1                   | None          | 1/2     |

| BREQ           | k               | Branch if equal                     | if (Z = 1) then PC ← PC + k + 1                                    | None          | 1/2     |

| BRNE           | k               | Branch if not equal                 | if (Z = 0) then PC $\leftarrow$ PC + k + 1                         | None          | 1/2     |

| BRCS           | k               | Branch if carry set                 | if (C = 1) then PC ← PC + k + 1                                    | None          | 1/2     |

| BRCC           | k               | Branch if carry cleared             | if (C = 0) then PC ← PC + k + 1                                    | None          | 1/2     |

| BRSH           | k               | Branch if same or higher            | if (C = 0) then PC ← PC + k + 1                                    | None          | 1/2     |

| BRLO           | k               | Branch if lower                     | if (C = 1) then PC ← PC + k + 1                                    | None          | 1/2     |

| BRMI           | k               | Branch if minus                     | if (N = 1) then PC ← PC + k + 1                                    | None          | 1/2     |

| BRPL           | k               | Branch if plus                      | if (N = 0) then PC ← PC + k + 1                                    | None          | 1/2     |

| BRGE           | k               | Branch if greater or equal, signed  | if (N $\oplus$ V= 0) then PC $\leftarrow$ PC + k + 1               | None          | 1/2     |

| BRLT           | k               | Branch if less than zero, signed    | if (N $\oplus$ V= 1) then PC $\leftarrow$ PC + k + 1               | None          | 1/2     |

| BRHS           | k               | Branch if half carry flag set       | if (H = 1) then PC ← PC + k + 1                                    | None          | 1/2     |

| BRHC           | k               | Branch if half carry flag cleared   | if (H = 0) then PC ← PC + k + 1                                    | None          | 1/2     |

| BRTS           | k               | Branch if T flag set                | if (T = 1) then PC ← PC + k + 1                                    | None          | 1/2     |

| BRTC           | k               | Branch if T flag cleared            | if (T = 0) then PC $\leftarrow$ PC + k + 1                         | None          | 1/2     |

| BRVS           | k               | Branch if overflow flag is set      | if (V = 1) then PC ← PC + k + 1                                    | None          | 1/2     |

| BRVC           | k               | Branch if overflow flag is cleared  | if (V = 0) then PC $\leftarrow$ PC + k + 1                         | None          | 1/2     |

| BRIE           | k               | Branch if interrupt enabled         | if (I = 1) then PC ← PC + k + 1                                    | None          | 1/2     |

| BRID           | k               | Branch if interrupt disabled        | if (I = 0) then PC $\leftarrow$ PC + k + 1                         | None          | 1/2     |

| Bit and Bit-te | st Instructions | s                                   |                                                                    |               |         |

| SBI            | P,b             | Set bit in I/O register             | I/O(P,b) ← 1                                                       | None          | 2       |

| CBI            | P,b             | Clear bit in I/O register           | I/O(P,b) ← 0                                                       | None          | 2       |

| LSL            | Rd              | Logical shift left                  | $Rd(n+1) \leftarrow Rd(n), Rd(0) \leftarrow 0$                     | Z, C, N, V    | 1       |

| LSR            | Rd              | Logical shift right                 | $Rd(n) \leftarrow Rd(n+1), Rd(7) \leftarrow 0$                     | Z, C, N, V    | 1       |

| ROL            | Rd              | Rotate left trough carry            | $Rd(0) \leftarrow C, Rd(n+1) \leftarrow Rd(n), C \leftarrow Rd(7)$ | Z, C, N, V    | 1       |

| ROR            | Rd              | Rotate right through carry          | $Rd(7) \leftarrow C, Rd(n) \leftarrow Rd(n+1), C \leftarrow Rd(0)$ | Z, C, N, V    | 1       |

| ASR            | Rd              | Arithmetic shift right              | $Rd(n) \leftarrow Rd(n+1), n=06$                                   | Z, C, N, V    | 1       |

| SWAP           | Rd              | Swap nibbles                        | $Rd(30) \leftarrow Rd(74), Rd(74) \leftarrow Rd(30)$               | None          | 1       |

| BSET           | S               | Flag set                            | SREG(s) ← 1                                                        | SREG(s)       | 1       |

| BCLR           | S               | Flag clear                          | SREG(s) ← 0                                                        | SREG(s)       | 1       |

| BST            | Rr, b           | Bit store from register to T        | $T \leftarrow Rr(b)$                                               | Т             | 1       |

| BLD            | Rd, b           | Bit load from T to register         | $Rd(b) \leftarrow T$                                               | None          | 1       |

# 3. Instruction Set Summary (Continued)

| <b>Mnemonics</b> | Operands       | Description                      | Operation                                  | Flags | #Clocks |

|------------------|----------------|----------------------------------|--------------------------------------------|-------|---------|

| SEC              |                | Set carry                        | C ← 1                                      | С     | 1       |

| CLC              |                | Clear carry                      | C ← 0                                      | С     | 1       |

| SEN              |                | Set negative flag                | N ← 1                                      | N     | 1       |

| CLN              |                | Clear negative flag              | N ← 0                                      | N     | 1       |

| SEZ              |                | Set zero flag                    | Z ← 1                                      | Z     | 1       |

| CLZ              |                | Clear zero flag                  | Z ← 0                                      | Z     | 1       |

| SEI              |                | Global interrupt enable          | I ← 1                                      | 1     | 1       |

| CLI              |                | Global interrupt disable         | I ← 0                                      | I     | 1       |

| SES              |                | Set signed test flag             | S ← 1                                      | S     | 1       |

| CLS              |                | Clear signed test flag           | S ← 0                                      | S     | 1       |

| SEV              |                | Set twos complement overflow.    | V ← 1                                      | V     | 1       |

| CLV              |                | Clear twos complement overflow   | V ← 0                                      | V     | 1       |

| SET              |                | Set T in SREG                    | T ← 1                                      | Т     | 1       |

| CLT              |                | Clear T in SREG                  | T ← 0                                      | Т     | 1       |

| SEH              |                | Set half carry flag in SREG      | H ← 1                                      | Н     | 1       |

| CLH              |                | Clear half carry flag in SREG    | H ← 0                                      | Н     | 1       |

| Data Transfe     | r Instructions |                                  |                                            |       |         |

| MOV              | Rd, Rr         | Move between registers           | Rd ← Rr                                    | None  | 1       |

| MOVW             | Rd, Rr         | Copy register word               | $Rd+1:Rd \leftarrow Rr+1:Rr$               | None  | 1       |

| LDI              | Rd, K          | Load immediate                   | Rd ← K                                     | None  | 1       |

| LD               | Rd, X          | Load indirect                    | $Rd \leftarrow (X)$                        | None  | 2       |

| LD               | Rd, X+         | Load indirect and post-inc.      | $Rd \leftarrow (X), X \leftarrow X + 1$    | None  | 2       |

| LD               | Rd, – X        | Load indirect and pre-dec.       | $X \leftarrow X - 1$ , Rd $\leftarrow (X)$ | None  | 2       |

| LD               | Rd, Y          | Load indirect                    | $Rd \leftarrow (Y)$                        | None  | 2       |

| LD               | Rd, Y+         | Load indirect and post-inc.      | $Rd \leftarrow (Y), Y \leftarrow Y + 1$    | None  | 2       |

| LD               | Rd, – Y        | Load indirect and pre-dec.       | $Y \leftarrow Y - 1$ , $Rd \leftarrow (Y)$ | None  | 2       |

| LDD              | Rd,Y+q         | Load indirect with displacement  | $Rd \leftarrow (Y + q)$                    | None  | 2       |

| LD               | Rd, Z          | Load indirect                    | $Rd \leftarrow (Z)$                        | None  | 2       |

| LD               | Rd, Z+         | Load indirect and post-inc.      | $Rd \leftarrow (Z), Z \leftarrow Z+1$      | None  | 2       |

| LD               | Rd, –Z         | Load indirect and pre-dec.       | $Z \leftarrow Z - 1$ , Rd $\leftarrow$ (Z) | None  | 2       |

| LDD              | Rd, Z+q        | Load indirect with displacement  | $Rd \leftarrow (Z + q)$                    | None  | 2       |

| LDS              | Rd, k          | Load direct from SRAM            | $Rd \leftarrow (k)$                        | None  | 2       |

| ST               | X, Rr          | Store indirect                   | (X) ← Rr                                   | None  | 2       |

| ST               | X+, Rr         | Store indirect and post-inc.     | (X) ← Rr, X ← X + 1                        | None  | 2       |

| ST               | – X, Rr        | Store indirect and pre-dec.      | $X \leftarrow X - 1$ , $(X) \leftarrow Rr$ | None  | 2       |

| ST               | Y, Rr          | Store indirect                   | (Y) ← Rr                                   | None  | 2       |

| ST               | Y+, Rr         | Store indirect and post-inc.     | $(Y) \leftarrow Rr, Y \leftarrow Y + 1$    | None  | 2       |

| ST               | – Y, Rr        | Store indirect and pre-dec.      | $Y \leftarrow Y - 1$ , $(Y) \leftarrow Rr$ | None  | 2       |

| STD              | Y+q,Rr         | Store indirect with displacement | (Y + q) ← Rr                               | None  | 2       |

| ST               | Z, Rr          | Store indirect                   | (Z) ← Rr                                   | None  | 2       |

# 3. Instruction Set Summary (Continued)

| Mnemonics   | Operands     | Description                      | Operation                                  | Flags | #Clocks |

|-------------|--------------|----------------------------------|--------------------------------------------|-------|---------|

| ST          | Z+, Rr       | Store indirect and post-inc.     | (Z) ← Rr, Z ← Z + 1                        | None  | 2       |

| ST          | –Z, Rr       | Store indirect and pre-dec.      | $Z \leftarrow Z - 1$ , $(Z) \leftarrow Rr$ | None  | 2       |

| STD         | Z+q,Rr       | Store indirect with displacement | (Z + q) ← Rr                               | None  | 2       |

| STS         | k, Rr        | Store direct to SRAM             | (k) ← Rr                                   | None  | 2       |

| LPM         |              | Load program memory              | R0 ← (Z)                                   | None  | 3       |

| LPM         | Rd, Z        | Load program memory              | $Rd \leftarrow (Z)$                        | None  | 3       |

| LPM         | Rd, Z+       | Load program memory and post-inc | $Rd \leftarrow (Z), Z \leftarrow Z+1$      | None  | 3       |

| SPM         |              | Store program memory             | (Z) ← R1:R0                                | None  | -       |

| IN          | Rd, P        | In port                          | $Rd \leftarrow P$                          | None  | 1       |

| OUT         | P, Rr        | Out port                         | P ← Rr                                     | None  | 1       |

| PUSH        | Rr           | Push register on stack           | STACK ← Rr                                 | None  | 2       |

| POP         | Rd           | Pop register from stack          | $Rd \leftarrow STACK$                      | None  | 2       |

| MCU Control | Instructions |                                  |                                            |       |         |

| NOP         |              | No operation                     |                                            | None  | 1       |

| SLEEP       |              | Sleep                            | (see specific descr. for sleep function)   | None  | 1       |

| WDR         |              | Watchdog reset                   | (see specific descr. for WDR/timer)        | None  | 1       |

| BREAK       |              | Break                            | For on-chip debug Only                     | None  | N/A     |

## 4. Register Summary

| Address | Name     | Bit 7    | Bit 6    | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1   | Bit 0   |

|---------|----------|----------|----------|----------|----------|----------|----------|---------|---------|

| (0xFF)  | Reserved | -        | -        | -        | -        | -        | -        | 1       | _       |

| (0xFE)  | Reserved | -        | -        | -        | -        | -        | -        | 1       | _       |

| (0xFD)  | Reserved | -        | -        | -        | -        | -        | -        | -       | _       |

| (0xFC)  | Reserved | -        | -        | -        | -        | -        | -        | -       | _       |

| (0xFB)  | Reserved | -        | -        | -        | -        | -        | -        | 1       | -       |

| (0xFA)  | CANMSG   | MSG 7    | MSG 6    | MSG 5    | MSG 4    | MSG 3    | MSG 2    | MSG 1   | MSG 0   |

| (0xF9)  | CANSTMPH | TIMSTM15 | TIMSTM14 | TIMSTM13 | TIMSTM12 | TIMSTM11 | TIMSTM10 | TIMSTM9 | TIMSTM8 |

| (0xF8)  | CANSTMPL | TIMSTM7  | TIMSTM6  | TIMSTM5  | TIMSTM4  | TIMSTM3  | TIMSTM2  | TIMSTM1 | TIMSTM0 |

| (0xF7)  | CANIDM1  | IDMSK28  | IDMSK27  | IDMSK26  | IDMSK25  | IDMSK24  | IDMSK23  | IDMSK22 | IDMSK21 |

| (0xF6)  | CANIDM2  | IDMSK20  | IDMSK19  | IDMSK18  | IDMSK17  | IDMSK16  | IDMSK15  | IDMSK14 | IDMSK13 |

| (0xF5)  | CANIDM3  | IDMSK12  | IDMSK11  | IDMSK10  | IDMSK9   | IDMSK8   | IDMSK7   | IDMSK6  | IDMSK5  |

| (0xF4)  | CANIDM4  | IDMSK4   | IDMSK3   | IDMSK2   | IDMSK1   | IDMSK0   | RTRMSK   | -       | IDEMSK  |

| (0xF3)  | CANIDT1  | IDT28    | IDT27    | IDT26    | IDT25    | IDT24    | IDT23    | IDT22   | IDT21   |

| (0xF2)  | CANIDT2  | IDT20    | IDT19    | IDT18    | IDT17    | IDT16    | IDT15    | IDT14   | IDT13   |

| (0xF1)  | CANIDT3  | IDT12    | IDT11    | IDT10    | IDT9     | IDT8     | IDT7     | IDT6    | IDT5    |

| (0xF0)  | CANIDT4  | IDT4     | IDT3     | IDT2     | IDT1     | IDT0     | RTRTAG   | RB1TAG  | RB0TAG  |

| (0xEF)  | CANCDMOB | CONMOB1  | CONMOB0  | RPLV     | IDE      | DLC3     | DLC2     | DLC1    | DLC0    |

| (0xEE)  | CANSTMOB | DLCW     | TXOK     | RXOK     | BERR     | SERR     | CERR     | FERR    | AERR    |

| (0xED)  | CANPAGE  | MOBNB3   | MOBNB2   | MOBNB1   | MOBNB0   | AINC     | INDX2    | INDX1   | INDX0   |

| (0xEC)  | CANHPMOB | HPMOB3   | HPMOB2   | HPMOB1   | НРМОВ0   | CGP3     | CGP2     | CGP1    | CGP0    |

| (0xEB)  | CANREC   | REC7     | REC6     | REC5     | REC4     | REC3     | REC2     | REC1    | REC0    |

| (0xEA)  | CANTEC   | TEC7     | TEC6     | TEC5     | TEC4     | TEC3     | TEC2     | TEC1    | TEC0    |

| (0xE9)  | CANTTCH  | TIMTTC15 | TIMTTC14 | TIMTTC13 | TIMTTC12 | TIMTTC11 | TIMTTC10 | TIMTTC9 | TIMTTC8 |

| (0xE8)  | CANTTCL  | TIMTTC7  | TIMTTC6  | TIMTTC5  | TIMTTC4  | TIMTTC3  | TIMTTC2  | TIMTTC1 | TIMTTC0 |

| (0xE7)  | CANTIMH  | CANTIM15 | CANTIM14 | CANTIM13 | CANTIM12 | CANTIM11 | CANTIM10 | CANTIM9 | CANTIM8 |

| (0xE6)  | CANTIML  | CANTIM7  | CANTIM6  | CANTIM5  | CANTIM4  | CANTIM3  | CANTIM2  | CANTIM1 | CANTIM0 |

| (0xE5)  | CANTCON  | TPRSC7   | TPRSC6   | TPRSC5   | TPRSC4   | TPRSC3   | TPRSC2   | TRPSC1  | TPRSC0  |

| (0xE4)  | CANBT3   | -        | PHS22    | PHS21    | PHS20    | PHS12    | PHS11    | PHS10   | SMP     |

| (0xE3)  | CANBT2   | -        | SJW1     | SJW0     | -        | PRS2     | PRS1     | PRS0    | -       |

| (0xE2)  | CANBT1   | -        | BRP5     | BRP4     | BRP3     | BRP2     | BRP1     | BRP0    | -       |

| (0xE1)  | CANSIT1  | -        | -        | -        | -        | -        | -        | -       | -       |

| (0xE0)  | CANSIT2  | _        | -        | SIT5     | SIT4     | SIT3     | SIT2     | SIT1    | SIT0    |

| (0xDF)  | CANIE1   | -        | -        | -        | -        | -        | -        | -       | -       |

Notes: 1. For compatibility with future devices, reserved bits should be written to zero if accessed. Reserved I/O memory addresses should never be written.

- 2. I/O registers within the address range 0x00 0x1F are directly bit-accessible using the SBI and CBI instructions. In these registers, the value of single bits can be checked by using the SBIS and SBIC instructions.

- 3. Some of the status flags are cleared by writing a logical one to them. Note that, unlike most other AVRs, the CBI and SBI instructions will only operate on the specified bit, and can therefore be used on registers containing such status flags. The CBI and SBI instructions work with registers 0x00 to 0x1F only.

- 4. When using the I/O specific commands IN and OUT, the I/O addresses 0x00 0x3F must be used. When addressing I/O Registers as data space using LD and ST instructions, 0x20 must be added to these addresses. The ATmega16/32/64/M1/C1 is a complex microcontroller with more peripheral units than can be supported within the 64 location reserved in Opcode for the IN and OUT instructions. For the Extended I/O space from 0x60 0xFF in SRAM, only the ST/STS/STD and LD/LDS/LDD instructions can be used.

- 5. These registers are only available on ATmega32/64M1. For other products described in this datasheet, these locations are reserved.

## 4. Register Summary (Continued)

| Address | Name     | Bit 7  | Bit 6  | Bit 5       | Bit 4       | Bit 3  | Bit 2   | Bit 1   | Bit 0   |

|---------|----------|--------|--------|-------------|-------------|--------|---------|---------|---------|

| (0xDE)  | CANIE2   | _      | _      | IEMOB5      | IEMOB4      | IEMOB3 | IEMOB2  | IEMOB1  | IEMOB0  |

| (0xDD)  | CANEN1   | _      | -      | -           | -           | -      | -       | -       | _       |

| (0xDC)  | CANEN2   | -      | -      | ENMOB5      | ENMOB4      | ENMOB3 | ENMOB2  | ENMOB1  | ENMOB0  |

| (0xDB)  | CANGIE   | ENIT   | ENBOFF | ENRX        | ENTX        | ENERR  | ENBX    | ENERG   | ENOVRT  |

| (0xDA)  | CANGIT   | CANIT  | BOFFIT | OVRTIM      | BXOK        | SERG   | CERG    | FERG    | AERG    |

| (0xD9)  | CANGSTA  | -      | OVRG   | -           | TXBSY       | RXBSY  | ENFG    | BOFF    | ERRP    |

| (0xD8)  | CANGCON  | ABRQ   | OVRQ   | TTC         | SYNTTC      | LISTEN | TEST    | ENA/STB | SWRES   |

| (0xD7)  | Reserved | -      | -      | -           | -           | -      | -       | -       | _       |

| (0xD6)  | Reserved | -      | -      | -           | -           | -      | _       | -       | _       |

| (0xD5)  | Reserved | _      | -      | -           | -           | -      | -       | -       | _       |

| (0xD4)  | Reserved | -      | -      | -           | -           | -      | -       | -       | -       |

| (0xD3)  | Reserved | -      | -      | -           | -           | -      | _       | -       | _       |

| (0xD2)  | LINDAT   | LDATA7 | LDATA6 | LDATA5      | LDATA4      | LDATA3 | LDATA2  | LDATA1  | LDATA0  |

| (0xD1)  | LINSEL   | -      | -      | -           | -           | /LAINC | LINDX2  | LINDX1  | LINDX0  |

| (0xD0)  | LINIDR   | LP1    | LP0    | LID5 / LDL1 | LID4 / LDL0 | LID3   | LID2    | LID1    | LID0    |

| (0xCF)  | LINDLR   | LTXDL3 | LTXDL2 | LTXDL1      | LTXDL0      | LRXDL3 | LRXDL2  | LRXDL1  | LRXDL0  |

| (0xCE)  | LINBRRH  | -      | -      | -           | -           | LDIV11 | LDIV10  | LDIV9   | LDIV8   |

| (0xCD)  | LINBRRL  | LDIV7  | LDIV6  | LDIV5       | LDIV4       | LDIV3  | LDIV2   | LDIV1   | LDIV0   |

| (0xCC)  | LINBTR   | LDISR  | -      | LBT5        | LBT4        | LBT3   | LBT2    | LBT1    | LBT0    |

| (0xCB)  | LINERR   | LABORT | LTOERR | LOVERR      | LFERR       | LSERR  | LPERR   | LCERR   | LBERR   |

| (0xCA)  | LINENIR  | _      | _      | -           | -           | LENERR | LENIDOK | LENTXOK | LENRXOK |

| (0xC9)  | LINSIR   | LIDST2 | LIDST1 | LIDST0      | LBUSY       | LERR   | LIDOK   | LTXOK   | LRXOK   |

| (0xC8)  | LINCR    | LSWRES | LIN13  | LCONF1      | LCONF0      | LENA   | LCMD2   | LCMD1   | LCMD0   |

| (0xC7)  | Reserved | -      | -      | -           | -           | -      | -       | -       | _       |

| (0xC6)  | Reserved | -      | -      | -           | -           | -      | -       | -       | _       |

| (0xC5)  | Reserved | -      | -      | -           | -           | -      | -       | -       | -       |

| (0xC4)  | Reserved | -      | -      | -           | -           | -      | -       | -       | _       |

| (0xC3)  | Reserved | -      | -      | -           | -           | -      | -       | -       | _       |

| (0xC2)  | Reserved | -      | -      | -           | -           | -      | -       | -       | -       |

| (0xC1)  | Reserved | -      | -      | -           | -           | -      | -       | -       | -       |

| (0xC0)  | Reserved | -      | -      | -           | -           | -      | -       | -       | -       |

| (0xBF)  | Reserved | -      | -      | -           | -           | -      | -       | -       | -       |

| (0xBE)  | Reserved | -      | -      | -           | -           | -      | -       | -       | -       |

Notes: 1. For compatibility with future devices, reserved bits should be written to zero if accessed. Reserved I/O memory addresses should never be written.

- 2. I/O registers within the address range 0x00 0x1F are directly bit-accessible using the SBI and CBI instructions. In these registers, the value of single bits can be checked by using the SBIS and SBIC instructions.

- 3. Some of the status flags are cleared by writing a logical one to them. Note that, unlike most other AVRs, the CBI and SBI instructions will only operate on the specified bit, and can therefore be used on registers containing such status flags. The CBI and SBI instructions work with registers 0x00 to 0x1F only.

- 4. When using the I/O specific commands IN and OUT, the I/O addresses 0x00 0x3F must be used. When addressing I/O Registers as data space using LD and ST instructions, 0x20 must be added to these addresses. The ATmega16/32/64/M1/C1 is a complex microcontroller with more peripheral units than can be supported within the 64 location reserved in Opcode for the IN and OUT instructions. For the Extended I/O space from 0x60 0xFF in SRAM, only the ST/STS/STD and LD/LDS/LDD instructions can be used.

- 5. These registers are only available on ATmega32/64M1. For other products described in this datasheet, these locations are reserved.

#### **Register Summary (Continued)** 4.

| Address               | Name     | Bit 7    | Bit 6    | Bit 5    | Bit 4    | Bit 3     | Bit 2     | Bit 1    | Bit 0    |

|-----------------------|----------|----------|----------|----------|----------|-----------|-----------|----------|----------|

| (0xBD)                | Reserved | -        | -        | -        | -        | -         | -         | -        | _        |

| (0xBC) <sup>(5)</sup> | PIFR     | -        | _        | -        | -        | PEV2      | PEV1      | PEV0     | PEOP     |

| (0xBB) <sup>(5)</sup> | PIM      | -        | -        | -        | _        | PEVE2     | PEVE1     | PEVE0    | PEOPE    |

| (0xBA) <sup>(5)</sup> | PMIC2    | POVEN2   | PISEL2   | PELEV2   | PFLTE2   | PAOC2     | PRFM22    | PRFM21   | PRFM20   |

| (0xB9) <sup>(5)</sup> | PMIC1    | POVEN1   | PISEL1   | PELEV1   | PFLTE1   | PAOC1     | PRFM12    | PRFM11   | PRFM10   |

| (0xB8) <sup>(5)</sup> | PMIC0    | POVEN0   | PISEL0   | PELEV0   | PFLTE0   | PAOC0     | PRFM02    | PRFM01   | PRFM00   |

| (0xB7) <sup>(5)</sup> | PCTL     | PPRE1    | PPRE0    | PCLKSEL  | -        | -         | _         | PCCYC    | PRUN     |

| (0xB6) <sup>(5)</sup> | POC      | -        | _        | POEN2B   | POEN2A   | POEN1B    | POEN1A    | POEN0B   | POEN0A   |

| (0xB5) <sup>(5)</sup> | PCNF     | -        | _        | PULOCK   | PMODE    | POPB      | POPA      | -        | _        |

| (0xB4) <sup>(5)</sup> | PSYNC    | -        | _        | PSYNC21  | PSYNC20  | PSYNC11   | PSYNC10   | PSYNC01  | PSYNC00  |

| (0xB3) <sup>(5)</sup> | POCR_RBH | -        | _        | -        | -        | POCR_RB11 | POCR_RB10 | POCR_RB9 | POCR_RB8 |

| (0xB2) <sup>(5)</sup> | POCR_RBL | POCR_RB7 | POCR_RB6 | POCR_RB5 | POCR_RB4 | POCR_RB3  | POCR_RB2  | POCR_RB1 | POCR_RB0 |

| (0xB1) <sup>(5)</sup> | POCR2SBH | -        | _        | -        | -        | POCR2SB11 | POCR2SB10 | POCR2SB9 | POCR2SB8 |

| (0xB0) <sup>(5)</sup> | POCR2SBL | POCR2SB7 | POCR2SB6 | POCR2SB5 | POCR2SB4 | POCR2SB3  | POCR2SB2  | POCR2SB1 | POCR2SB0 |

| (0xAF) <sup>(5)</sup> | POCR2RAH | -        | _        | -        | -        | POCR2RA11 | POCR2RA10 | POCR2RA9 | POCR2RA8 |

| (0xAE) <sup>(5)</sup> | POCR2RAL | POCR2RA7 | POCR2RA6 | POCR2RA5 | POCR2RA4 | POCR2RA3  | POCR2RA2  | POCR2RA1 | POCR2RA0 |

| (0xAD) <sup>(5)</sup> | POCR2SAH | -        | _        | -        | -        | POCR2SA11 | POCR2SA10 | POCR2SA9 | POCR2SA8 |

| (0xAC) <sup>(5)</sup> | POCR2SAL | POCR2SA7 | POCR2SA6 | POCR2SA5 | POCR2SA4 | POCR2SA3  | POCR2SA2  | POCR2SA1 | POCR2SA0 |

| (0xAB) <sup>(5)</sup> | POCR1SBH | -        | _        | -        | -        | POCR1SB11 | POCR1SB10 | POCR1SB9 | POCR1SB8 |

| (0xAA) <sup>(5)</sup> | POCR1SBL | POCR1SB7 | POCR1SB6 | POCR1SB5 | POCR1SB4 | POCR1SB3  | POCR1SB2  | POCR1SB1 | POCR1SB0 |

| (0xA9) <sup>(5)</sup> | POCR1RAH | -        | _        | -        | -        | POCR1RA11 | POCR1RA10 | POCR1RA9 | POCR1RA8 |

| (0xA8) <sup>(5)</sup> | POCR1RAL | POCR1RA7 | POCR1RA6 | POCR1RA5 | POCR1RA4 | POCR1RA3  | POCR1RA2  | POCR1RA1 | POCR1RA0 |

| (0xA7) <sup>(5)</sup> | POCR1SAH | -        | _        | -        | -        | POCR1SA11 | POCR1SA10 | POCR1SA9 | POCR1SA8 |

| (0xA6) <sup>(5)</sup> | POCR1SAL | POCR1SA7 | POCR1SA6 | POCR1SA5 | POCR1SA4 | POCR1SA3  | POCR1SA2  | POCR1SA1 | POCR1SA0 |

| (0xA5) <sup>(5)</sup> | POCR0SBH | -        | _        | -        | -        | POCR0SB11 | POCR0SB10 | POCR0SB9 | POCR0SB8 |

| (0xA4) <sup>(5)</sup> | POCR0SBL | POCR0SB7 | POCR0SB6 | POCR0SB5 | POCR0SB4 | POCR0SB3  | POCR0SB2  | POCR0SB1 | POCR0SB0 |

| (0xA3) <sup>(5)</sup> | POCR0RAH | -        | -        | -        | -        | POCR0RA11 | POCR0RA10 | POCR0RA9 | POCR0RA8 |

| (0xA2) <sup>(5)</sup> | POCR0RAL | POCR0RA7 | POCR0RA6 | POCR0RA5 | POCR0RA4 | POCR0RA3  | POCR0RA2  | POCR0RA1 | POCR0RA0 |

| (0xA1) <sup>(5)</sup> | POCR0SAH | -        | -        | -        | -        | POCR0SA11 | POCR0SA10 | POCR0SA9 | POCR0SA8 |

| (0xA0) <sup>(5)</sup> | POCR0SAL | POCR0SA7 | POCR0SA6 | POCR0SA5 | POCR0SA4 | POCR0SA3  | POCR0SA2  | POCR0SA1 | POCR0SA0 |

| (0x9F)                | Reserved | -        | -        | -        | _        | -         | _         | -        | -        |

| (0x9E)                | Reserved | -        | -        | -        | _        | -         | _         | -        | -        |

| (0x9D)                | Reserved | -        | -        | -        | _        | -         | _         | -        | -        |

1. For compatibility with future devices, reserved bits should be written to zero if accessed. Reserved I/O memory Notes: addresses should never be written.

- 2. I/O registers within the address range 0x00 0x1F are directly bit-accessible using the SBI and CBI instructions. In these registers, the value of single bits can be checked by using the SBIS and SBIC instructions.

- 3. Some of the status flags are cleared by writing a logical one to them. Note that, unlike most other AVRs, the CBI and SBI instructions will only operate on the specified bit, and can therefore be used on registers containing such status flags. The CBI and SBI instructions work with registers 0x00 to 0x1F only.

- 4. When using the I/O specific commands IN and OUT, the I/O addresses 0x00 0x3F must be used. When addressing I/O Registers as data space using LD and ST instructions, 0x20 must be added to these addresses. The ATmega16/32/64/M1/C1 is a complex microcontroller with more peripheral units than can be supported within the 64 location reserved in Opcode for the IN and OUT instructions. For the Extended I/O space from 0x60 - 0xFF in SRAM, only the ST/STS/STD and LD/LDS/LDD instructions can be used.

- 5. These registers are only available on ATmega32/64M1. For other products described in this datasheet, these locations are reserved.

## 4. Register Summary (Continued)

| Address | Name     | Bit 7          | Bit 6      | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1       | Bit 0       |

|---------|----------|----------------|------------|----------|----------|----------|----------|-------------|-------------|

| (0x9C)  | Reserved | -              | -          | -        | -        | -        | -        | -           | _           |

| (0x9B)  | Reserved | -              | -          | -        | -        | -        | -        | -           | _           |

| (0x9A)  | Reserved | -              | -          | -        | -        | -        | -        | -           | _           |

| (0x99)  | Reserved | -              | -          | -        | -        | -        | -        | -           | _           |

| (0x98)  | Reserved | -              | -          | -        | -        | -        | -        | -           | -           |

| (0x97)  | AC3CON   | AC3EN          | AC3IE      | AC3IS1   | AC3IS0   | -        | AC3M2    | AC3M1       | AC3M0       |

| (0x96)  | AC2CON   | AC2EN          | AC2IE      | AC2IS1   | AC2IS0   | -        | AC2M2    | AC2M1       | AC2M0       |

| (0x95)  | AC1CON   | AC1EN          | AC1IE      | AC1IS1   | AC1IS0   | AC1ICE   | AC1M2    | AC1M1       | AC1M0       |

| (0x94)  | AC0CON   | AC0EN          | AC0IE      | AC0IS1   | AC0IS0   | ACCKSEL  | AC0M2    | AC0M1       | AC0M0       |

| (0x93)  | Reserved | -              | -          | -        | -        | -        | -        | -           | -           |

| (0x92)  | DACH     | - / DAC9       | - / DAC8   | - / DAC7 | - / DAC6 | - / DAC5 | - / DAC4 | DAC9 / DAC3 | DAC8 / DAC2 |

| (0x91)  | DACL     | DAC7 /<br>DAC1 | DAC6 /DAC0 | DAC5 / - | DAC4 / - | DAC3 / - | DAC2 / - | DAC1/-      | DAC0 /      |

| (0x90)  | DACON    | DAATE          | DATS2      | DATS1    | DATS0    | -        | DALA     | DAOE        | DAEN        |

| (0x8F)  | Reserved | -              | -          | -        | -        | -        | -        | -           | _           |

| (0x8E)  | Reserved | -              | -          | -        | -        | -        | -        | -           | _           |

| (0x8D)  | Reserved | -              | -          | -        | -        | -        | -        | -           | _           |

| (0x8C)  | Reserved | -              | -          | -        | -        | ı        | ı        | -           | ı           |

| (0x8B)  | OCR1BH   | OCR1B15        | OCR1B14    | OCR1B13  | OCR1B12  | OCR1B11  | OCR1B10  | OCR1B9      | OCR1B8      |

| (0x8A)  | OCR1BL   | OCR1B7         | OCR1B6     | OCR1B5   | OCR1B4   | OCR1B3   | OCR1B2   | OCR1B1      | OCR1B0      |

| (0x89)  | OCR1AH   | OCR1A15        | OCR1A14    | OCR1A13  | OCR1A12  | OCR1A11  | OCR1A10  | OCR1A9      | OCR1A8      |

| (0x88)  | OCR1AL   | OCR1A7         | OCR1A6     | OCR1A5   | OCR1A4   | OCR1A3   | OCR1A2   | OCR1A1      | OCR1A0      |

| (0x87)  | ICR1H    | ICR115         | ICR114     | ICR113   | ICR112   | ICR111   | ICR110   | ICR19       | ICR18       |

| (0x86)  | ICR1L    | ICR17          | ICR16      | ICR15    | ICR14    | ICR13    | ICR12    | ICR11       | ICR10       |

| (0x85)  | TCNT1H   | TCNT115        | TCNT114    | TCNT113  | TCNT112  | TCNT111  | TCNT110  | TCNT19      | TCNT18      |

| (0x84)  | TCNT1L   | TCNT17         | TCNT16     | TCNT15   | TCNT14   | TCNT13   | TCNT12   | TCNT11      | TCNT10      |

| (0x83)  | Reserved | -              | -          | -        | -        | -        | -        | -           | 1           |

| (0x82)  | TCCR1C   | FOC1A          | FOC1B      | -        | -        | -        | -        | -           | -           |

| (0x81)  | TCCR1B   | ICNC1          | ICES1      | -        | WGM13    | WGM12    | CS12     | CS11        | CS10        |

| (0x80)  | TCCR1A   | COM1A1         | COM1A0     | COM1B1   | COM1B0   | ı        | ı        | WGM11       | WGM10       |

| (0x7F)  | DIDR1    | -              | AMP2PD     | ACMP0D   | AMP0PD   | AMP0ND   | ADC10D   | ADC9D       | ADC8D       |

| (0x7E)  | DIDR0    | ADC7D          | ADC6D      | ADC5D    | ADC4D    | ADC3D    | ADC2D    | ADC1D       | ADC0D       |

| (0x7D)  | Reserved | -              | -          | -        | -        | -        | -        | -<br>-      | -           |

Notes: 1. For compatibility with future devices, reserved bits should be written to zero if accessed. Reserved I/O memory addresses should never be written.

- 2. I/O registers within the address range 0x00 0x1F are directly bit-accessible using the SBI and CBI instructions. In these registers, the value of single bits can be checked by using the SBIS and SBIC instructions.

- 3. Some of the status flags are cleared by writing a logical one to them. Note that, unlike most other AVRs, the CBI and SBI instructions will only operate on the specified bit, and can therefore be used on registers containing such status flags. The CBI and SBI instructions work with registers 0x00 to 0x1F only.

- 4. When using the I/O specific commands IN and OUT, the I/O addresses 0x00 0x3F must be used. When addressing I/O Registers as data space using LD and ST instructions, 0x20 must be added to these addresses. The ATmega16/32/64/M1/C1 is a complex microcontroller with more peripheral units than can be supported within the 64 location reserved in Opcode for the IN and OUT instructions. For the Extended I/O space from 0x60 0xFF in SRAM, only the ST/STS/STD and LD/LDS/LDD instructions can be used.

- 5. These registers are only available on ATmega32/64M1. For other products described in this datasheet, these locations are reserved.

## **Register Summary (Continued)**

| Address     | Name     | Bit 7          | Bit 6       | Bit 5    | Bit 4    | Bit 3    | Bit 2    | Bit 1       | Bit 0       |

|-------------|----------|----------------|-------------|----------|----------|----------|----------|-------------|-------------|

| (0x7C)      | ADMUX    | REFS1          | REFS0       | ADLAR    | -        | MUX3     | MUX2     | MUX1        | MUX0        |

| (0x7B)      | ADCSRB   | ADHSM          | ISRCEN      | AREFEN   | -        | ADTS3    | ADTS2    | ADTS1       | ADTS0       |

| (0x7A)      | ADCSRA   | ADEN           | ADSC        | ADATE    | ADIF     | ADIE     | ADPS2    | ADPS1       | ADPS0       |

| (0x79)      | ADCH     | - / ADC9       | - / ADC8    | - / ADC7 | - / ADC6 | - / ADC5 | - / ADC4 | ADC9 / ADC3 | ADC8 / ADC2 |

| (0x78)      | ADCL     | ADC7 /<br>ADC1 | ADC6 / ADC0 | ADC5 / - | ADC4 / - | ADC3 / - | ADC2 / - | ADC1 / -    | ADC0 /      |

| (0x77)      | AMP2CSR  | AMP2EN         | AMP2IS      | AMP2G1   | AMP2G0   | AMPCMP2  | AMP2TS2  | AMP2TS1     | AMP2TS0     |

| (0x76)      | AMP1CSR  | AMP1EN         | AMP1IS      | AMP1G1   | AMP1G0   | AMPCMP1  | AMP1TS2  | AMP1TS1     | AMP1TS0     |

| (0x75)      | AMP0CSR  | AMP0EN         | AMP0IS      | AMP0G1   | AMP0G0   | AMPCMP0  | AMP0TS2  | AMP0TS1     | AMP0TS0     |

| (0x74)      | Reserved | -              | -           | -        | -        | -        | -        | -           | -           |

| (0x73)      | Reserved | -              | -           | -        | _        | -        | -        | -           | -           |

| (0x72)      | Reserved | -              | _           | -        | -        | -        | -        | _           | -           |

| (0x71)      | Reserved | -              | -           | -        | -        | -        | _        | -           | -           |

| (0x70)      | Reserved | -              | -           | -        | -        | -        | -        | -           | -           |

| (0x6F)      | TIMSK1   | -              | -           | ICIE1    | -        | -        | OCIE1B   | OCIE1A      | TOIE1       |