# 0.200" 8-Character 5x7 Dot Matrix Parallel Input Alphanumeric Intelligent Display® Devices

Lead (Pb) Free Product - RoHS Compliant

Red HSDP2110S

Yellow HSDP2111S

High Efficiency Red HSDP2112S

Green HSDP2113S

High Efficiency Green HSDP2114S

Soft Orange HSDP2115S

#### DESCRIPTION

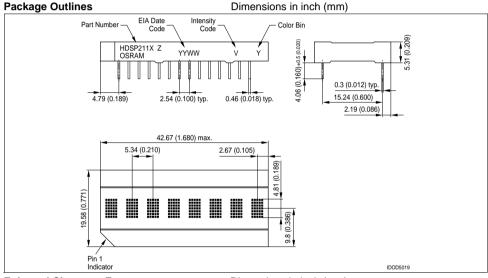

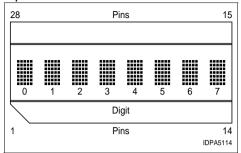

The HDSP2110S (Red), HDSP2111S (Yellow), HDSP2112S (High Efficiency Red), HDSP2113S (Green), HDSP2114S (High Efficiency Green), and HDSP2115S (Soft Orange) are eight digit, 5 x 7 dot matrix, alphanumeric Intelligent Display devices. The 0.20 inch high digits are packaged in a rugged, high quality, optically transparent, 0.6 inch lead spacing, 28 pin plastic DIP.

The on-board CMOS has a built-in 128 character ROM. The HDSP211XS also has a user definable character (UDC) feature, which uses a RAM that permits storage of 16 arbitrary characters, symbols or icons that are software-definable by the user. The character ROM itself is mask programmable and easily modified by the manufacturer to provide specified custom characters.

The HDSP211XS is designed for standard microprocessor interface techniques, and is fully TTL compatible. The Clock I/O and Clock Select pins allow the user to cascade multiple display modules.

#### **FEATURES**

- Eight 0.200" Dot Matrix Characters in Red, Yellow, High Efficiency Red, Green, High Efficiency Green, or Soft Orange

- Built-in 128 Character ROM, Mask Programmable for Custom Fonts

- Readable from 8 Feet (2.5 meters)

- Built-in Decoders, Multiplexers and Drivers

- Wide Viewing Angle, X Axis ± 55°, Y Axis ± 65°

- Programmable Features:

- Individual Flashing Character

- Full Display Blinking

- Multi-Level Dimming and Blanking

- Clear Function

- Self Test

1

- · Internal or External Clock

- End Stackable Dual-In-Line Plastic Package

- · Read/Write Capability

- · 16 User Definable Characters

ESD Warning: Standard p

Standard precautions for CMOS handling should be observed.

### **Ordering Information**

| Туре      | Color of Emission     | Character Height [inch] ([mm]) | Ordering Code |

|-----------|-----------------------|--------------------------------|---------------|

| HSDP2110S | red                   |                                | Q68000A8560   |

| HSDP2111S | yellow                |                                | Q68000A8561   |

| HSDP2112S | high efficiency red   | 0.200 (5.40)                   | Q68000A8562   |

| HSDP2113S | green                 | 0.200 (5.10)                   | Q68000A8563   |

| HSDP2114S | high efficiency green |                                | Q68000A8564   |

| HSDP2115S | soft orange           |                                | Q68000A8907   |

### Maximum Ratings at 25°C

| Parameter                                                                    | Symbol           | Value                     | Unit |

|------------------------------------------------------------------------------|------------------|---------------------------|------|

| Operating temperature range                                                  | $T_{\sf op}$     | - 40 <b>+</b> 85          | °C   |

| Storage temperature range                                                    | $T_{stg}$        | - 40 <b>+</b> 100         | °C   |

| DC Supply Voltage, $V_{\rm CC}$ to GND (max. voltage with no LEDs on)        | $V_{\sf CC}$     | -0.3 to + 7.0             | V    |

| Input Voltage Levels All inputs                                              |                  | -0.3 to $V_{\rm CC}$ +0.3 | V    |

| Operating Voltage, $V_{\rm CC}$ to GND (max. voltage with 20 dots/digits on) |                  | + 5.5                     | V    |

| Solder temperature 063" (1.59 mm) below seating plane, t < 5.0 s             | $T_{\mathbb{S}}$ | 260                       | °C   |

| Relative Humidity at 85°C (non-condensing)                                   |                  | 85                        | %    |

| ESD (100 pF, 1.5 kΩ), each pin                                               | V <sub>Z</sub>   | 4.0                       | kV   |

### Optical Characteristics at 25°C

$(V_{11} = V_{CC} = 5.0 \text{ V} \text{ at } 100\% \text{ brightness level, viewing angle: X axis } \pm 55^{\circ}, \text{ Y axis } \pm 65^{\circ})$

| Description             |                  | Symbol                  |                  | Values              |                                  |                    |                                    |                          |                    |  |

|-------------------------|------------------|-------------------------|------------------|---------------------|----------------------------------|--------------------|------------------------------------|--------------------------|--------------------|--|

|                         |                  |                         | Red<br>HSDP2110S | Yellow<br>HSDP2111S | High Efficiency Red<br>HSDP2112S | Green<br>HSDP2113S | High Efficiency Green<br>HSDP2114S | Soft Orange<br>HSDP2115S |                    |  |

| Peak Luminous Intensity | (min.)<br>(typ.) | I <sub>Vpeak</sub>      | 70<br>90         | 130<br>210          | 150<br>330                       | 150<br>260         | 200<br>510                         | 150<br>270               | μcd/dot<br>μcd/dot |  |

| Peak Wavelength         | (typ.)           | $\lambda_{\text{peak}}$ | 660              | 583                 | 630                              | 565                | 568                                | 610                      | nm                 |  |

| Dominant Wavelength     | (typ.)           | $\lambda_{\text{dom}}$  | 639              | 585                 | 620                              | 570                | 574                                | 604                      | nm                 |  |

Note:

3

<sup>1)</sup> Peak luminous intensity is measured at  $T_A = T_J = 25$ °C. No time is allowed for the device to warm up prior to measurement.

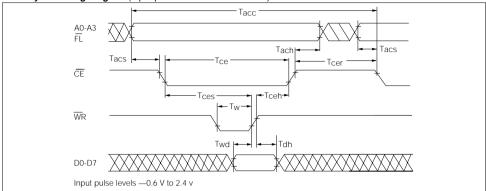

### Write Cycle Timing Diagram (Input pulse levels -0.6 V to 2.4 V)

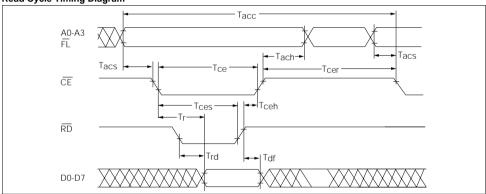

### **Read Cycle Timing Diagram**

### **Switching Specifications**

(over operating temperature range and  $V_{\rm CC}$ =4.5 V)

| Symbol           | Description                                      | Min. | Units | Symbol           | Description                                          | Min. | Units |

|------------------|--------------------------------------------------|------|-------|------------------|------------------------------------------------------|------|-------|

| T <sub>acc</sub> | Display Access Time—Write                        | 210  | ns    | $T_{\rm dh}$     | Data Write Time                                      | 20   | ns    |

| T <sub>acc</sub> | Display Access Time—Read                         | 230  | ns    | $T_{\rm r}$      | Chip Enable Active Prior to Valid Data               | 160  | ns    |

| T <sub>acs</sub> | Address Setup Time to CE                         | 10   | ns    | $T_{\rm rd}$     | Read Active Prior to Valid Data                      | 95   | μs    |

| T <sub>ce</sub>  | Chip Enable Active Time—Write                    | 140  | ns    | $T_{\rm df}$     | Read Data Float Delay                                | 10   | ns    |

| T <sub>ce</sub>  | Chip Enable Active Time—Read                     | 160  | ns    | $T_{rc}$         | Reset Active Time                                    | 300  | ns    |

| T <sub>ach</sub> | Address Hold Time to CE                          | 20   | ns    | $T_{\rm w}$      | Write Active Time                                    | 100  | ns    |

| T <sub>ces</sub> | Chip Enable Active Prior to<br>Rising Edge—Write | 140  | ns    | $T_{ m wd}$      | Data Valid Prior to<br>Rising Edge of Write Signal   | 50   | ns    |

| T <sub>ces</sub> | Chip Enable Active Prior to<br>Rising Edge—Read  | 160  | ns    | T <sub>ceh</sub> | Chip Enable Hold to Rising Edge of Read/Write Signal | 0    | ns    |

| T <sub>cer</sub> | Chip Enable Recovery Time                        | 60   | ns    |                  |                                                      |      |       |

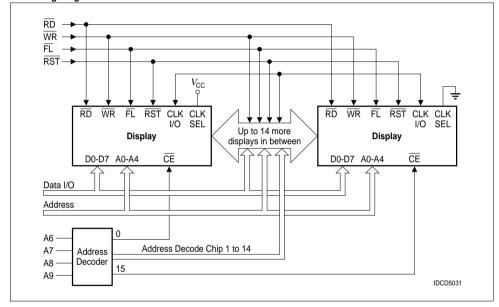

#### **Cascading Displays**

The HDSP211XS oscillator is designed to drive up to 16 other HDSP211XSs with input loading of 15 pF each.

The following are the general requirements for cascading 16 displays together:

- · Determine the correct address for each display.

- · Use CE from an address decoder to select the correct display.

- Select one of the Displays to provide the clock for the other displays. Connect CLKSEL to  $V_{\rm CC}$  for this display.

- · Tie CLKSEL to ground on other displays.

- Use RTS to synchronize the blinking between the displays.

**Cascading Diagram**

OSRAM

### Electrical Characteristics at 25°C

| Parameters                                                | Limits      |       |                         | Conditions |                                                                                                 |

|-----------------------------------------------------------|-------------|-------|-------------------------|------------|-------------------------------------------------------------------------------------------------|

|                                                           | Min.        | Тур.  | Max.                    | Units      |                                                                                                 |

| V <sub>cc</sub>                                           | 4.5         | 5.0   | 5.5                     | V          | _                                                                                               |

| I <sub>CC</sub> Blank                                     | _           | 0.65  | 1.0                     | mA         | V <sub>CC</sub> =5.0 V, V <sub>IN</sub> =5.0 V                                                  |

| I <sub>CC</sub> 12 dots/digit on <sup>(1) (2)</sup>       | _           | 185   | 255                     | mA         | V <sub>CC</sub> =5.0 V, "V" in all 8 digits                                                     |

| I <sub>CC</sub> 20 dots/digit on <sup>(1) (2)</sup>       | _           | 284   | 370                     | mA         | V <sub>CC</sub> =5.0 V, "#" in all 8 digits                                                     |

| I <sub>ILP</sub> (with pull-up)<br>Input Leakage          | -18         | -11   | -5.0                    | μА         | $V_{\text{CC}}$ =5.0 V, $V_{\text{IN}}$ =0 V to $V_{\text{CC}}$ , (WR, CE, FL, RST, RD, CLKSEL) |

| I <sub>IL</sub> (no pull-up) Input Leakage                | -1.0        | _     | +1.0                    | μΑ         | V <sub>CC</sub> =5.0 V, V <sub>IN</sub> =0-5 V,<br>(CLK, A0-A3, D0-D7)                          |

| V <sub>IH</sub><br>Input Voltage High                     | 2.0         | _     | V <sub>CC</sub><br>+0.3 | V          | V <sub>CC</sub> =4.5 V to 5.5 V                                                                 |

| V <sub>IL</sub> Input Voltage Low                         | GND<br>-0.3 | _     | _                       | V          | V <sub>CC</sub> =4.5 V to 5.5 V                                                                 |

| V <sub>OL</sub> (D0–D7), Output Voltage Low               | _           | _     | 0.4                     | V          | V <sub>CC</sub> =4.5 V, I <sub>OL</sub> =1.6 mA                                                 |

| V <sub>OL</sub> (CLK), Output Voltage Low                 | _           | _     | 0.4                     | V          | $V_{\rm CC}$ =4.5 V, $I_{\rm OL}$ = 40 $\mu {\rm A}$                                            |

| V <sub>OH</sub> Output Voltage High                       | 2.4         | _     | _                       | V          | $V_{\rm CC}$ =4.5 V, $I_{\rm OH}$ = -40 $\mu {\rm A}$                                           |

| $\theta_{\text{JC}}$ Thermal Resistance, Junction to Case | _           | 25    | _                       | °C/W       | _                                                                                               |

| Clock I/O Frequency                                       | 28          | 57.34 | 81.14                   | kHz        | V <sub>CC</sub> =4.5 to 5.5 V                                                                   |

| FM, Digit Multiplex Frequency                             | 125         | 256   | 362.5                   | Hz         | V <sub>CC</sub> =4.5 to 5.5 V                                                                   |

| Blinking Rate                                             | 0.98        | 2.0   | 2.83                    | Hz         | _                                                                                               |

| Clock I/O Buss Loading                                    | _           | _     | 2.40                    | pF         | _                                                                                               |

| Clock Out Rise Time                                       | _           | _     | 500                     | nsec       | $V_{\rm CC}$ =4.5 V, $V_{\rm OH}$ =2.4 V                                                        |

| Clock Out Fall Time                                       | _           | _     | 500                     | nsec       | V <sub>CC</sub> =4.5 V, V <sub>OH</sub> =0.4 V                                                  |

## Recommended Operating Conditions ( $T_A$ =-40°C to +85°C)

| Parameter           | Symbol          | Min. | Max. | Units |

|---------------------|-----------------|------|------|-------|

| Supply Voltage      | V <sub>CC</sub> | 4.5  | 5.5  | V     |

| Input Voltage Low   | V <sub>IL</sub> | _    | 0.8  | V     |

| Input Voltage High  | V <sub>IH</sub> | 2.0  | _    | V     |

| Output Voltage Low  | V <sub>OL</sub> | _    | 0.4  | V     |

| Output Voltage High | V <sub>OH</sub> | 2.4  | _    | V     |

<sup>)</sup>  $I_{\rm CC}$  is an average value. <sup>2)</sup>  $I_{\rm CC}$  is measured with the display at full brightness. Peak  $I_{\rm CC}$  =<sup>28</sup> $I_{\rm 15}$   $I_{\rm CC}$  average (#displayed).

### **Top View**

### Pin Assignment

| Pin | Function        | Definition                                                                 | Pin | Function   | Definition                                                                                                    |

|-----|-----------------|----------------------------------------------------------------------------|-----|------------|---------------------------------------------------------------------------------------------------------------|

| 1   | RST             | Used to initialize a display and sychronize blinking for multiple displays | 15  | GND supply | Analog Ground for LED drivers                                                                                 |

| 2   | FL              | Low input accesses the Flash RAM                                           | 16  | GND logic  | Digital Ground for internal drivers                                                                           |

| 3   | A0              | Address input LSB                                                          | 17  | CE         | Enables access to the display                                                                                 |

| 4   | A1              | Address input                                                              | 18  | RD         | A low will read data from the display if $\overline{\text{CE}}$ is low. If read from display is not required, |

| 5   | A2              | Address input MSB                                                          | 19  | D0         | Data input LSB                                                                                                |

| 6   | A3              | Mode selector                                                              | 20  | D1         | Data input                                                                                                    |

| 7   | V <sub>CC</sub> |                                                                            | 21  | No pin     | _                                                                                                             |

| 8   | V <sub>CC</sub> | Optional connection to positive power supply input.                        | 22  | No pin     | _                                                                                                             |

| 9   | V <sub>CC</sub> |                                                                            | 23  | D2         | Data input                                                                                                    |

| 10  | A4              | Mode Selector                                                              | 24  | D3         | Data input                                                                                                    |

| 11  | CLKSEL          | Selects internal/high clock source                                         | 25  | D4         | Data input                                                                                                    |

| 12  | CLK I/O         | Outputs master clock or inputs external clock                              | 26  | D5         | Data input                                                                                                    |

| 13  | WR              | A low will write data into the display if $\overline{\text{CE}}$ is low    | 27  | D6         | Data input                                                                                                    |

| 14  | V <sub>cc</sub> | Positive power supply input                                                | 28  | D7         | Data input MSB, selects ROM, page 1 or 2                                                                      |

### **Character Set**

|    |    |     |    | D0  | L        | Н        | L        | Н        | L          | Н        | L        | Н        | L        | Н                                       | L           | Н         | L         | Н         | L         | Н         |

|----|----|-----|----|-----|----------|----------|----------|----------|------------|----------|----------|----------|----------|-----------------------------------------|-------------|-----------|-----------|-----------|-----------|-----------|

|    | AS | CII |    | D1  | L        | L        | Н        | Н        | L          | L        | Н        | Н        | L        | L                                       | Н           | Н         | L         | L         | Н         | Н         |

|    | CO | DE  |    | D2  | L        | L        | L        | L        | Н          | Н        | Н        | Н        | L        | L                                       | L           | L         | Н         | Н         | Н         | Н         |

|    |    |     |    | D3  | L        | L        | L        | L        | L          | L        | L        | L        | Н        | Н                                       | Н           | Н         | Н         | Н         | Н         | Н         |

| D7 | D6 | D5  | D4 | HEX | 0        | 1        | 2        | 3        | 4          | 5        | 6        | 7        | 8        | 9                                       | Α           | В         | С         | D         | Е         | F         |

| L  | L  | L   | L  | 0   |          | ::::     | :::      |          |            |          | ::       | :::      |          | :··;                                    |             |           | <u></u> : | ••••      | :::       | ::        |

| L  | L  | L   | Н  | 1   | ·:··     | ::::     |          |          | :::        |          |          |          |          |                                         | ::          | ;.        | ::        | ·:·       |           | ••••      |

| L  | L  | н   | L  | 2   |          |          | ::       | ••••     |            | •••      |          | :        | :        | :                                       | <b>::</b> : | ••••      | ::        | ••••      | ::        |           |

| L  | L  | н   | Н  | 3   |          |          |          | •        |            | ••••     | :::      | :        |          |                                         | ::          | ::        | •••       | ••••      | •         | ••••      |

| L  | Н  | L   | L  | 4   |          |          |          | ••••     |            |          |          |          |          | ::                                      |             |           |           |           |           |           |

| L  | Н  | L   | Н  | 5   | :        |          |          | ••••     | ••••       |          | •        |          |          | • • •                                   |             |           | ٠.        | •••       | ·••.      | ••••      |

| L  | Н  | н   | L  | 6   | ::       |          |          | ···.     |            |          |          | •        |          | ::::::::::::::::::::::::::::::::::::::: | :           |           | ••••••    |           |           |           |

| L  | Н  | н   | Н  | 7   |          | :::      |          | •        | <b>:</b> . |          |          |          | ×        | ·:·                                     |             |           | •••••     | :         | ٠         |           |

| Н  | х  | х   | х  | 8   | UDC<br>0 | UDC<br>1 | UDC<br>2 | UDC<br>3 | UDC<br>4   | UDC<br>5 | UDC<br>6 | UDC<br>7 | UDC<br>8 | UDC<br>9                                | UDC<br>10   | UDC<br>11 | UDC<br>12 | UDC<br>13 | UDC<br>14 | UDC<br>15 |

IDCS5086

#### Notes:

- 1. Upon power up, the device will initialize in a random state.

- 2. X=don't care.

**OSRAM**

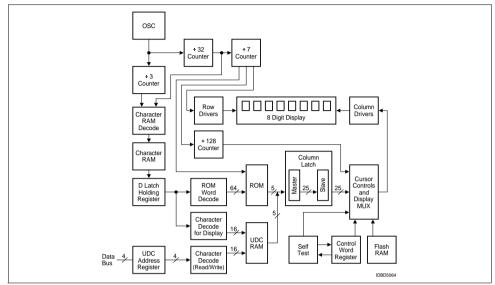

### **Block Diagram**

#### **Functional Description**

The display's user interface is organized into five memory areas. They are accessed using the Flash Input,  $\overline{FL}$ , and address lines, A3 and A4. All the listed RAMs and Registers may be read or written through the data bus. See Table "Memory Selection". Each input pin is described in Pin Definitions.

### **Five Basic Memory Areas**

| Character RAM                                              | Stores either ASCII (Katakana) character data or an UDC RAM address                                                      |

|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| Flash RAM                                                  | 1 x 8 RAM which stores Flash data                                                                                        |

| User-Defined<br>Character RAM<br>(UDC RAM)                 | Stores dot pattern for custom characters                                                                                 |

| User-Defined Address<br>Register (UDC Address<br>Register) | Provides address to UDC RAM when user is writing or reading custom character                                             |

| Control Word<br>Register                                   | Enables adjustment of display<br>brightness, flash individual<br>characters, blink, self test or clearing<br>the display |

RST can be used to initialize display operation upon power up or during normal operation. When activated, RST will clear the Flash RAM and Control Word Register (00H) and reset the internal counter. All eight display memory locations will be set to 20H to show blanks in all digits.

FL pin enables access to the Flash RAM. The Flash RAM will set (D0=1) or reset (D0=0) flashing of the character addressed by A0–A2.

The 1 x 8 bit **Control Word Register** is loaded with attribute data if A3=0.

The **Control Word Logic** decodes attribute data for proper implementation.

**Character ROM** is designed for 128 ASCII characters. The ROM is Mask Programmable for custom fonts.

The **Clock Source** could either be the internal oscillator (CLKSEL=1) of the device or an external clock (CLKSEL=0) could be an input from another HDSP211X display for the synchronization of blinking for multiple displays.

The **Display Multiplexer** controls the Row Drivers so no additional logic is required for a display system.

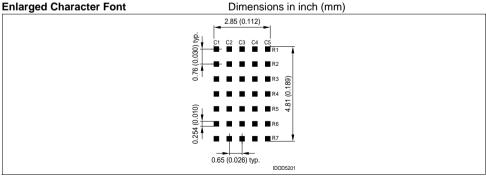

The **Display** has eight digits. Each digit has 35 LEDs clustered into a 5 x 7 dot matrix.

#### **Memory Selection**

| FL | A4 | А3 | Section of Memory     | A2-A0             | Data Bits Used |

|----|----|----|-----------------------|-------------------|----------------|

| 0  | Χ  | X  | Flash RAM             | Character Address | D0             |

| 1  | 0  | 0  | UDC Address Register  | Don't Care        | D3-D0          |

| 1  | 0  | 1  | UDC RAM               | Row Address       | D4-D0          |

| 1  | 1  | 1  | Character RAM         | Character Address | D7-D0          |

| 1  | 1  | 0  | Control Word Register | Don't Care        | D7-D0          |

#### Theory of operation

The HDSP211XS Programmable Display is designed to work with all major microprocessors. Data entry is via an eight bit parallel bus. Three bits of address route the data to the proper digit location in the RAM. Standard control signals like WR and CE allow the data to be written into the display.

D0–D7 data bits are used for both Character RAM and control word data input. A3 acts as the mode selector.

If A3=1, character RAM is selected. Then input data bit D7 will determine whether input data bits D0–D6 is ASCII coded data (D7=0) or UDC data (D7=1). See section on UDC Address Register and RAM.

For normal operation  $\overline{FL}$  pin should be held high. When  $\overline{FL}$  is held low, Flash RAM is accessed to set character blinking.

The seven bit ASCII code is decoded by the Character ROM to generate Column data. Twenty columns worth of data is sent out each display cycle, and it takes fourteen display cycles to write into eight digits.

The rows are multiplexed in two sets of seven rows each. The internal timing and control logic synchronizes the turning on of rows and presentation of column data to assure proper display operation.

#### Power Up Sequence

Upon power up display will come on at random. Thus the display should be reset on power-up. The reset will clear the Flash RAM, Control Word Register and reset the internal counter. All the digits will show blanks and display brightness level will be 100%.

The display must not be accessed until three clock pulses (110 µseconds minimum using the internal clock) after the rising edge of the reset line.

#### Microprocessor interface

The interface to a microprocessor is through the 8-bit data bus (D0–D7), the 4-bit address bus (A0–A3) and control lines  $\overline{FL}$ ,  $\overline{CE}$  and  $\overline{WR}$ .

To write data (ASCII/Control Word) into the display  $\overline{\text{CE}}$  should be held low, address and data signals stable and  $\overline{\text{WR}}$  should be brought low. The data is written on the low to high transition of  $\overline{\text{WD}}$

The Control Word is decoded by the Control Word Decode Logic. Each code has a different function. The code for display brightness changes the duty cycle for the column drivers. The peak LED current stays the same but the average LED current diminishes depending on the intensity level.

The character Flash Enable causes 2.0 Hz coming out of the counter to be ANDED with column drive signal and makes the column driver to cycle at 2.0 Hz. Thus the character flashes at 2.0 Hz.

The display Blink works the same way as the Flash Enable but causes all twenty column drivers to cycle at 2.0 Hz thereby making all eight digits to blink at 2.0 Hz.

The Self Test function of the IC consists of two internal routines which exercise major portions of the IC and illuminates all the

Clear bit clears the character RAM and writes a blank into the display memory. It however does not clear the control word.

ASCII Data or Control Word Data can be written into the display at this point. For multiple display operation, CLK I/O must be properly selected. CLK I/O will output the internal clock if CLKSEL=1, or will allow input from an external clock if CLKSEL=0.

#### Character RAM

The Character RAM is selected when FL, A4 and A3 are set to 1,1,1 during a read or write cycle. The Character RAM is a 8 by 8 bit RAM with each of the eight locations corresponding to a digit on the display. Digit 0 is on the left side of the display and digit 7 is on the right side of the display. Address lines, A2–A0 select the digit address with A2 being the most significant bit and A0 being the least significant bit. The two types of data stored in the Character RAM are the ASCII coded data and the UDC Address Data. The type of data stored in the Character RAM is determined by data bit, D7. If D7 is low, then ASCII coded data is stored in data bits D6–D0. If D7 is high, then UDC Address Data is stored in data bit D3–D0.

The ASCII coded data is a 7 bit code used to select one of 128 ASCII characters permanently stored in the ASCII ROM.

The UDC Address data is a 4 bit code used to select one of the UDC characters in the UDC RAM. There are up to 16 characters available. See Table "Character RAM Access Logic" (page 11).

### UDC Address Register and UDC RAM

The UDC Address Register and UDC RAM allows the user to generate and store up to 16 custom characters. Each custom character is defined in 5 x 7 dot matrix pattern. It takes 8 write cycles to define a custom character, one cycle to load the UDC Address Register and 7 cycles to define the character. The contents of the UDC Address Register will store the 4 bit address for one of the 16 UDC RAM locations. The UDC RAM is used to store the custom character.

#### **UDC Address Register**

The UDC Address Register is selected by setting FL=1, A4=0, A3=0. It is a 4 bit register and uses data bits, D3=D0 to store the 4 bit address code (D7=D4 are ignored). The address code selects one of 16 UDC RAM locations for custom character generation.

#### UDC RAM

The UDC RAM is selected by setting  $\overline{FL}$ =1, A4=0, A3=1. The RAM is comprised of a 7 x 5 bit RAM. As shown in Table "Flash RAM Access Logic" (page 12), address lines, A2–A0 select one of the 7 rows of the custom character. Data bits, D4–D0 determine the 5 bits of column data in each row. Each data bit corresponds to a LED. If the data bit is high, then the LED is on If the data bit is low, the LED is off. To create a character, each of the 7 rows of column data need to be defined. See Tables "UDCAddress Register and UDC Character RAM" (page 11) and "UDC Character Map" (page 12) for logic.

#### Flash RAM

The Flash RAM allows the display to flash one or more of the characters being displayed. The Flash Ram is accessed by setting FL low. A4 and A3 are ignored. The Flash RAM is a 8 x 1 bit RAM with each bit corresponding to a digit address. Digit 0 is on the left side of the display and digit 7 is on the right side of the display. Address lines, A2–A0 select the digit address with A2 being the most significant digit and A0 being the least significant digit. Data bit, D0, sets and resets the flash bit for each digit. When D0 is high, the flash bit is set and when D0 is low, It is reset. See Table "Flash RAM Access Logic" (page 12).

#### Control Word

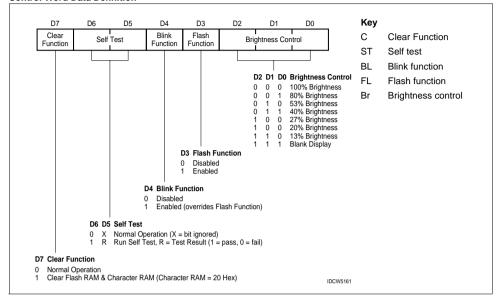

The Control Word is used to set up the attributes required by the user. It is addressed by setting  $\overline{F}L=1$ , A4=1, A3=0. The Control Word is an 8 bit register and is accessed using data bits, D7–D0. See Table "Control Word Access Logic" (page 12) and Figure "Control Word Data Definition" (page 13) for the logic and attributed control. The Control Word has 5 functions. They are brightness control, flashing character enable, blinking character enable, self test, and clear (Flash and Character RAMS only).

#### **Brightness Control**

Control Word bits, D2–D0, control the brightness of the display with a binary code of 000 being 100% brightness and 111 being display blank. See Figure "Control Word Data Definition" (page 13) for brightness level versus binary code. The average  $l_{\rm CC}$  can be calculated by multiplying the 100% brightness level  $l_{\rm CC}$  value by the display's brightness level. For example, a display set to 80% brightness with a 100% average  $l_{\rm CC}$  value of 200 mA will have an average  $l_{\rm CC}$  value of 200 mA x 80%=160 mA.

#### Flash Function

Control Word bit, D3, enables or disables the Flash Function. When D3 is 1, the Flash Function is enabled and any digit with its corresponding bit set in the Flash RAM will flash at approximately 2.0 Hz. When using an external clock, the flash rate can be determined by dividing the clock rate by 28,672. When D3 is 0, the Flash Function is disabled and the contents of the Flash RAM is ignored. For synchronized flashing on multiple displays, see the Reset Section (page 12).

#### Character RAM Access Logic

| RST | CE | WR | RD | FL | A4 | А3 | A2 A1 A0                         | D7 D6 D5 D4 D3 D2 D1 D0                     |

|-----|----|----|----|----|----|----|----------------------------------|---------------------------------------------|

| 1   | 0  | 0  | 1  | 1  | 1  | 1  | Character Address for Digits 0-7 | 0 7 bit ASCII code for a Write Cycle        |

| 1   | 0  | 1  | 0  | 1  | 1  | 1  | Character Address for Digits 0-7 | 0 7 bit ASCII code read during a Read Cycle |

| 1   | 0  | 0  | 1  | 1  | 0  | 0  | Character Address for Digits 0-7 | 1 D3-D0=UDC address for a Write Cycle       |

| 1   | 0  | 1  | 0  | 1  | 0  | 0  | Character Address for Digits 0-7 | 1 D3-D0=UDC address for Read Data           |

#### **UDC Address Register and UDC Character RAM**

| RST | CE | WR | RD | FL | A4 | А3 | A2 A1 A0                             | D7 D6 D5 D4 D3 D2 D1 D0                              |                            |

|-----|----|----|----|----|----|----|--------------------------------------|------------------------------------------------------|----------------------------|

| 1   | 0  | 0  | 1  | 1  | 0  | 0  | Not used for UDC<br>Address Register | D3-D0=UDC RAM Address Code for Write Cycle           | UDC<br>Address<br>Register |

| 1   | 0  | 1  | 0  | 1  | 0  | 0  | Not used for UDC<br>Address Register | D3-D0=UDC RAM Address Code for Read Cycle            |                            |

| 1   | 0  | 0  | 1  | 1  | 0  | 1  | A2-A0=Character<br>Row Address       | D4–D0=Character Column Data for<br>Write Cycle       | UDC<br>RAM                 |

| 1   | 0  | 1  | 0  | 1  | 0  | 1  | A2–A0=Character<br>Row Address       | D4–D0=Character Column Data read during a Read Cycle |                            |

11

#### **Blink Function**

Control Word bit, D4, enables or disables the Blink Function. When D4 is 1, the Blink Function is enabled and all characters on the display will blink at approximately 2.0 Hz. The Blink Function will override the Flash Function if both functions are enabled. When D4 is 0, the Blink Function is disabled. When using an external clock, the blink rate can be determined by dividing the clock rate by 28,672. For synchronized blinking on multiple displays, see the Reset Section.

#### Self Test

Before starting Self Test, Reset must first be activated. Control Word bits, D6 and D5, are used for the Self Test Function. When D6 is 1, the Self Test is initiated. Results of the Self Test are stored in bits D5. Control Word bit, D5, is a read only bit. When D5 is 1, Self Test passed is indicated. When D5 is 0, Self Test failed is indicated. The Self Test function of the IC consists of two internal routines which exercise major portions of the IC and illuminates all of the LEDs. The first routine cycles the ASCII decoder ROM through all states and performs a check sum on the output. If the check sum agrees with the correct value, D5 is set to a 1.

#### **UDC Character Map**

| Row | Data |    |      | Column Data |         |    |    |    |  |  |  |  |

|-----|------|----|------|-------------|---------|----|----|----|--|--|--|--|

|     |      |    |      | C1          | C2      | СЗ | C4 | C5 |  |  |  |  |

| A2  | A1   | A0 | Row# | D4          | D3      | D2 | D1 | D0 |  |  |  |  |

| 0   | 0    | 0  | 1    |             |         |    |    |    |  |  |  |  |

| 0   | 0    | 1  | 2    |             |         |    |    |    |  |  |  |  |

| 0   | 1    | 0  | 3    | 5 x 7       | ,       |    |    |    |  |  |  |  |

| 0   | 1    | 1  | 4    | Dot         | Matrix  |    |    |    |  |  |  |  |

| 1   | 0    | 0  | 5    | Patte       | Pattern |    |    |    |  |  |  |  |

| 1   | 0    | 1  | 6    |             |         |    |    |    |  |  |  |  |

| 1   | 1    | 0  | 7    |             |         |    |    |    |  |  |  |  |

The second routine provides a visual test of the LEDs using the drive circuitry. This is accomplished by writing checkered and inverse checkered patterns to the display. Each pattern is displayed for approximately 2.0 seconds. During the self test function the display must not be accessed. The time needed to execute the self test function is calculated by multiplying the clock time by 262,144 (typical time = 4.6 sec.). At the end of the self test function, the Character RAM is loaded with blanks; the Control Word Register is set to zeroes except D5, and the Flash RAM is cleared and the UDC Address Register is set to all 1.0 s.

Clear Function (see Table "Clear Function" (page 13) and Figure "Control Word Data Definition" (page 13))

Control Word bit, D7 clears the character RAM to 20 hex and the flash RAM to all zeroes. The RAMs are cleared within three clock cycles (110 µs minimum, using the internal clock) when D7 is set to 1. During the clear time the display must not be accessed. When the clear function is finished, bit 7 of the Control Word RAM will be reset to a "0".

#### Reset Function

The display should be reset on power up of the display (RST=LOW). When the display is reset, the Character RAM, Flash RAM, and Control Word Register are cleared.

The display's internal counters are reset. Reset cycle takes three clock cycles (110 µseconds minimum using the internal clock). The display must not be accessed during this time.

To synchronize the flashing and blinking of multiple displays, it is necessary for the display to use a common clock source and reset all the displays at the same time to start the internal counters at the same place.

While  $\overline{\text{RST}}$  is low, the display must not be accessed by RD nor  $\overline{\text{WR}}$

#### Flash RAM Access Logic

| RST | CE | WR | RD | FL | A4 | А3 | A2 A1 A0                            | D7 D6 D5 D4 D3 D2 D1 D0                                 |

|-----|----|----|----|----|----|----|-------------------------------------|---------------------------------------------------------|

| 1   | 0  | 0  | 1  | 0  | Х  | Х  | Flash RAM Address<br>for Digits 0–7 | D0=Flash Data, 0-Flash Off and 1=Flash On (Write Cycle) |

| 1   | 0  | 1  | 0  | 0  | Х  | Х  | Flash RAM Address<br>for Digits 0–7 | D0=Flash Data, 0-Flash Off and 1=Flash On (Read Cycle)  |

#### Control Word Access Logic

| RST | CE | WR | RD | FL | A4 | А3 | A2 A1 A0                  | D7 D6 D5 D4 D3 D2 D1 D0                                                                           |

|-----|----|----|----|----|----|----|---------------------------|---------------------------------------------------------------------------------------------------|

| 1   | 0  | 0  | 1  | 1  | 1  | 0  | Not used for Control Word | Control Word data for a Write Cycle, see Figure "Control Word Data Definition" ( <i>page 13</i> ) |

| 1   | 0  | 1  | 0  | 1  | 1  | 0  | Not used for Control Word | Control Word data for a Read during a Read Cycle                                                  |

#### **Control Word Data Definition**

#### Clear Function

| CE | WR | FL | AL | А3 | A2 | A1 | Α0 | D7 | D6 | D5 | D4 | D3 | D2 | D1     | D0 | Operation                                                            |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|--------|----|----------------------------------------------------------------------|

| 0  | 0  | 1  | 1  | 0  | X  | X  | X  | 0  | X  | X  | X  | X  | X  | X<br>X | X  | Clear disabled<br>Clear user RAM, page RAM,<br>flash RAM and display |

X=don't care

#### Display Cycle Using Built-in ROM Example

Display message "Showtime." Digit 0 is leftmost—closest to pin 1. Logic levels: 0=Low, 1=High, X=Don't care

| RST | CE | WR | RD | FL | A4 | А3 | A2 | A1 | A0 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Operation                                     | Display   |

|-----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|-----------------------------------------------|-----------|

| 0   | Х  | 1  | 1  | 1  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Х  | Reset. No Read/Write<br>Within 3 Clock Cycles | All Blank |

| 1   | 0  | 0  | 1  | 1  | 1  | 0  | Х  | Х  | Х  | 0  | 0  | Х  | 0  | 0  | 0  | 1  | 1  | 53% Brightness<br>Selected                    | All Blank |

| 1   | 0  | 0  | 1  | 1  | 1  | 1  | 0  | 0  | 0  | 0  | 1  | 0  | 1  | 0  | 0  | 1  | 1  | Write "S" to Digit 0                          | S         |

| 1   | 0  | 0  | 1  | 1  | 1  | 1  | 0  | 0  | 1  | 0  | 1  | 0  | 0  | 1  | 0  | 0  | 0  | Write "H" to Digit 1                          | SH        |

| 1   | 0  | 0  | 1  | 1  | 1  | 1  | 0  | 1  | 0  | 0  | 1  | 0  | 0  | 1  | 1  | 1  | 1  | Write "O" to Digit 2                          | SHO       |

| 1   | 0  | 0  | 1  | 1  | 1  | 1  | 0  | 1  | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 1  | 1  | Write "W" to Digit 3                          | SHOW      |

| 1   | 0  | 0  | 1  | 1  | 1  | 1  | 1  | 0  | 0  | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 0  | Write "T" to Digit 4                          | SHOWT     |

| 1   | 0  | 0  | 1  | 1  | 1  | 1  | 1  | 0  | 1  | 0  | 1  | 0  | 0  | 1  | 0  | 0  | 1  | Write "I" to Digit 5                          | SHOWTI    |

| 1   | 0  | 0  | 1  | 1  | 1  | 1  | 1  | 1  | 0  | 0  | 1  | 0  | 0  | 1  | 1  | 0  | 1  | Write "M" to Digit 6                          | SHOWTIM   |

| 1   | 0  | 0  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 0  | 1  | 0  | 0  | 0  | 1  | 0  | 1  | Write "E" to Digit 7                          | SHOWTIME  |

#### Displaying User Defined Character Example

Load character "A" into UDC-5 and then display it in digit 2 Logic levels: 0=Low, 1=High, X=Don't care

| RST | CE | WR | RD | FL | A4 | А3 | A2 | <b>A1</b> | A0 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Operation                                     | Display     |

|-----|----|----|----|----|----|----|----|-----------|----|----|----|----|----|----|----|----|----|-----------------------------------------------|-------------|

| 0   | Х  | 1  | 1  | 1  | Х  | Х  | Х  | Х         | Х  | Х  | Х  | х  | Х  | Х  | Х  | Х  | Х  | Reset. No Read/Write<br>Within 3 Clock Cycles | All Blank   |

| 1   | 0  | 0  | 1  | 1  | 0  | 0  | Х  | Х         | Х  | Х  | Х  | Х  | Х  | 0  | 1  | 0  | 1  | Select UDC-5                                  | All Blank   |

| 1   | 0  | 0  | 1  | 1  | 0  | 1  | 0  | 0         | 0  | Х  | Х  | Х  | 0  | 1  | 1  | 1  | 0  | Write into Row 1 of UDC-5                     | All Blank   |

| 1   | 0  | 0  | 1  | 1  | 0  | 1  | 0  | 0         | 1  | Х  | Х  | Х  | 1  | 0  | 0  | 0  | 1  | Write into Row 2 of UDC-5                     | All Blank   |

| 1   | 0  | 0  | 1  | 1  | 0  | 1  | 0  | 1         | 0  | Х  | Х  | Х  | 1  | 0  | 0  | 0  | 1  | Write into Row 3 of UDC-5                     | All Blank   |

| 1   | 0  | 0  | 1  | 1  | 0  | 1  | 0  | 1         | 1  | Х  | Х  | Х  | 1  | 1  | 1  | 1  | 1  | Write into Row 4 of UDC-5                     | All Blank   |

| 1   | 0  | 0  | 1  | 1  | 0  | 1  | 1  | 0         | 0  | Х  | Х  | Х  | 1  | 0  | 0  | 0  | 1  | Write into Row 5 of UDC-5                     | All Blank   |

| 1   | 0  | 0  | 1  | 1  | 0  | 1  | 1  | 0         | 1  | Х  | Х  | Х  | 1  | 0  | 0  | 0  | 1  | Write into Row 6 of UDC-5                     | All Blank   |

| 1   | 0  | 0  | 1  | 1  | 0  | 1  | 1  | 1         | 0  | Х  | Х  | Х  | 1  | 0  | 0  | 0  | 1  | Write into Row 7 of UDC-5                     | All Blank   |

| 1   | 0  | 0  | 1  | 1  | 1  | 1  | 0  | 1         | 0  | 1  | Х  | Х  | Х  | 0  | 1  | 0  | 1  | Write UDC-5 into Digit 2                      | (Digit 2) A |

#### Electrical and Mechanical Considerations Voltage Transient Suppression

For best results power the display and the components that interface with the display to avoid logic inputs higher than  $V_{\rm CC}$ . Additionally, the LEDs may cause transients in the power supply line while they change display states. The common practice is to place a parallel combination of a 0.01  $\mu$ F and a 22  $\mu$ F capacitor between  $V_{\rm CC}$  and GND for all display packages.

#### **ESD Protection**

The input protection structure of the HDSP211XS provides significant protection against ESD damage. It is capable of withstanding discharges greater than 2.0 kV. Take all the standard precautions, normal for CMOS components. These include properly grounding personnel, tools, tables, and transport carriers that come in contact with unshielded parts. If these conditions are not, or cannot be met, keep the leads of the device shorted together or the parts in antistatic packaging.

#### **Soldering Considerations**

The HDSP211XS can be hand soldered with SN63 solder using a grounded iron set to 260  $^{\circ}\text{C}.$

Wave soldering is also possible following these conditions: Preheat that does not exceed 93°C on the solder side of the PC board or a package surface temperature of 85°C. Water soluble organic acid flux (except carboxylic acid) or rosin-based RMA flux without alcohol can be used.

Direct contact with alcohol or alcohol vapor will cause degradation of the package.

Wave temperature of 245°C ±5°C with a dwell between 1.5 sec. to 3.0 sec. Exposure to the wave should not exceed temperatures above 260°C for five seconds at 0.063° below the seating plane. The packages should not be immersed in the wave.

#### Post Solder Cleaning Procedures

The least offensive cleaning solution is hot D.I. water (60°C) for less than 15 minutes. Addition of mild saponifiers is acceptable. Do not use commercial dishwasher detergents.

For faster cleaning, solvents may be used. Exercise care in choosing solvents as some may chemically attack the nylon package. Maximum exposure should not exceed two minutes at elevated temperatures. Acceptable solvents are TF (trichorotrifluorethane), TA, 111 Trichloroethane, and unheated acetone. (1)

#### Note:

Acceptable commercial solvents are: Basic TF, Arklone, P. Genesolv, D. Genesolv DA, Blaco-Tron TF and Blaco-Tron TA.

Unacceptable solvents contain alcohol, methanol, methylene chloride, ethanol, TP35, TCM, TMC, TMS+, TE, or TES. Since many commercial mixtures exist, contact a solvent vendor for chemical composition information. Some major solvent manufacturers are: Allied Chemical Corporation, Specialty Chemical Division, Morristown, NJ; Baron-Blakeslee, Chicago, IL; Dow Chemical, Midland, MI; E.I. DuPont de Nemours & Co., Wilmington, DE.

For further information refer to Appnotes 18 and 19 at www.osram-os.com

An alternative to soldering and cleaning the display modules is to use sockets. Naturally, 28 pin DIP sockets.600" wide with .100" centers work well for single displays. Multiple display assemblies are best handled by longer SIP sockets or DIP sockets when available for uniform package alignment. Socket manufacturers are Aries Electronics, Inc., Frenchtown, NJ; Garry Manufacturing, New Brunswick, NJ; Robinson-Nugent, New Albany, IN; and Samtec Electronic Hardward, New Albany, IN.

For further information refer to Appnote 22 at www.osram-os.com

**OSRAM**

#### **Optical Considerations**

The .200" high character of the HDSP211XS gives readability up to eight feet. Proper filter selection enhances readability over this distance

Using filters emphasizes the contrast ratio between a lit LED and the character background. This will increase the discrimination of different characters. The only limitation is cost. Take into consideration the ambient lighting environment for the best cost/benefit ratio for filters.

Incandescent (with almost no green) or fluorescent (with almost no red) lights do not have the flat spectral response of sunlight. Plastic band-pass filters are an inexpensive and effective way to strengthen contrast ratios. The HDSP2110/2112S are red/high efficiency red displays and should be matched with long wavelength pass filter in the 570 nm to 590 nm range. The HDSP2113S should be matched with a yellow-green band-pass filter that peaks at 565 nm. For displays of multiple colors, neutral density grey filters offer the best compromise.

Additional contrast enhancement is gained by shading the displays. Plastic band-pass filters with built-in louvers offer the next step up in contrast improvement. Plastic filters can be improved further with anti-reflective coatings to reduce glare. The trade-off is fuzzy characters. Mounting the filters close to the display reduces this effect. Take care not to overheat the plastic filter by allowing for proper air flow.

Optimal filter enhancements are gained by using circular polarized, anti-reflective, band-pass filters. The circular polarizing further enhances contrast by reducing the light that travels through the filter and reflects back off the display to less than 1%.

Several filter manufacturers supply quality filter materials. Some of them are: Panelgraphic Corporation, W. Caldwell, NJ; SGL Homalite, Wilmington, DE; 3M Company, Visual Products Division, St. Paul, MN; Polaroid Corporation, Polarizer Division, Cambridge, MA; Marks Polarized Corporation, Deer Park, NY, Hoya Optics, Inc., Fremont, CA.

One last note on mounting filters: recessing displays and bezel assemblies is an inexpensive way to provide a shading effect in overhead lighting situations. Several bezel manufacturers are: R.M.F. Products, Baklava, IL; Nobody Components, Griffith Plastic Corp., Burningly, CA; Photo Chemical Products of California, Santa Monica, CA; I.E.E.-Atlas, Van Nuys, CA.

**Revision History: 2006-01-23** Previous Version: 2004-11-11

| Page | Subjects (major changes since last revision) | Date of change |

|------|----------------------------------------------|----------------|

| all  | Lead free device                             | 2006-01-23     |

|      |                                              |                |

|      |                                              |                |

| -    |                                              |                |

| -    |                                              |                |

| -    |                                              |                |

|      |                                              |                |

|      |                                              |                |

Published by OSRAM Opto Semiconductors GmbH Wernerwerkstrasse 2, D-93049 Regensburg www.osram-os.com © All Rights Reserved.

#### Attention please!

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved. Due to technical requirements components may contain dangerous substances. For information on the types in question please contact our Sales Organization. If printed or downloaded, please find the latest version in the Internet.

#### Packing

Please use the recycling operators known to you. We can also help you – get in touch with your nearest sales office. By agreement we will take packing material back, if it is sorted. You must bear the costs of transport. For packing material that is returned to us unsorted or which we are not obliged to accept, we shall have to invoice you for any costs incurred.

Components used in life-support devices or systems must be expressly authorized for such purpose! Critical components<sup>1)</sup> may only be used in life-support devices or systems<sup>2)</sup> with the express written approval of OSRAM OS.

- A critical component is a component used in a life-support device or system whose failure can reasonably be expected to cause the failure of that life-support device or system, or to affect its safety or the effectiveness of that device or system.

- 2) Life support devices or systems are intended (a) to be implanted in the human body, or (b) to support and/or maintain and sustain human life. If they fail, it is reasonable to assume that the health and the life of the user may be endangered.